# **Master Computer Science**

G-ALP: Rethinking GPU Decompression of Light-Weight Encodings

Name: Sven Hielke Hepkema

Student ID: 2454556

Date: 12/05/2025

Specialisation: Advanced Computing and Sys-

tems

1st supervisor: Prof. Dr. Stefan Manegold

2nd supervisor: Prof. Dr. Peter Boncz

Daily supervisor: Azim Afroozeh

Master's Thesis in Computer Science

Leiden Institute of Advanced Computer Science (LIACS)

Leiden University Niels Bohrweg 1

2333 CA Leiden 2

The Netherlands

# Contents

| 1 | Inti                                | roduction                                           | 1          |  |  |  |  |

|---|-------------------------------------|-----------------------------------------------------|------------|--|--|--|--|

|   | 1.1                                 | Research Questions                                  | 5          |  |  |  |  |

|   | 1.2                                 | Outline                                             | 5          |  |  |  |  |

| 2 | Bac                                 | Background                                          |            |  |  |  |  |

|   | 2.1                                 | Compression                                         | 7          |  |  |  |  |

|   | 2.2                                 | FastLanes                                           | 8          |  |  |  |  |

|   | 2.3                                 | Compression on GPUs                                 | 10         |  |  |  |  |

|   | 2.4                                 | nvCOMP                                              | 11         |  |  |  |  |

| 3 | NVIDIA Graphics Processing Units 13 |                                                     |            |  |  |  |  |

|   | 3.1                                 | Execution model                                     | 13         |  |  |  |  |

|   | 3.2                                 | Memory                                              | 16         |  |  |  |  |

|   | 3.3                                 | Warps                                               | 18         |  |  |  |  |

|   | 3.4                                 | Compute capability                                  | 19         |  |  |  |  |

|   | 3.5                                 | Occupancy                                           | 21         |  |  |  |  |

|   | 3.6                                 | Assembly                                            | 22         |  |  |  |  |

|   | 3.7                                 | Microbenchmark: Heterogeneous Instruction Pipelines | 23         |  |  |  |  |

|   | 3.8                                 | Microbenchmark: Instruction-Level Parallelism       |            |  |  |  |  |

| 4 | GP                                  | U Decoding Algorithms                               | <b>3</b> 0 |  |  |  |  |

|   | 4.1                                 | FastLanes Decoding                                  | 30         |  |  |  |  |

|   |                                     | 4.1.1 Single Value Decoding                         | 31         |  |  |  |  |

|   |                                     | 4.1.2 Branchless Single Value Decoding              | 33         |  |  |  |  |

|   | 4.2                                 | ALP Decoding                                        | 34         |  |  |  |  |

|   |                                     | 4.2.1 Single Value Decoding                         | 34         |  |  |  |  |

|   |                                     | 4.2.2 Data-Parallel Exception Patching              | 35         |  |  |  |  |

|   |                                     | 4.2.3 Buffering                                     | 38         |  |  |  |  |

| 5 | Ber                                 | achmarks                                            | 39         |  |  |  |  |

|   | 5.1                                 | Preliminaries                                       | 39         |  |  |  |  |

|   |                                     | 5.1.1 Benchmarking Setup                            | 39         |  |  |  |  |

|              |                                                      | 5.1.2  | Filter Benchmark                                 | 39 |

|--------------|------------------------------------------------------|--------|--------------------------------------------------|----|

|              |                                                      | 5.1.3  | API                                              | 40 |

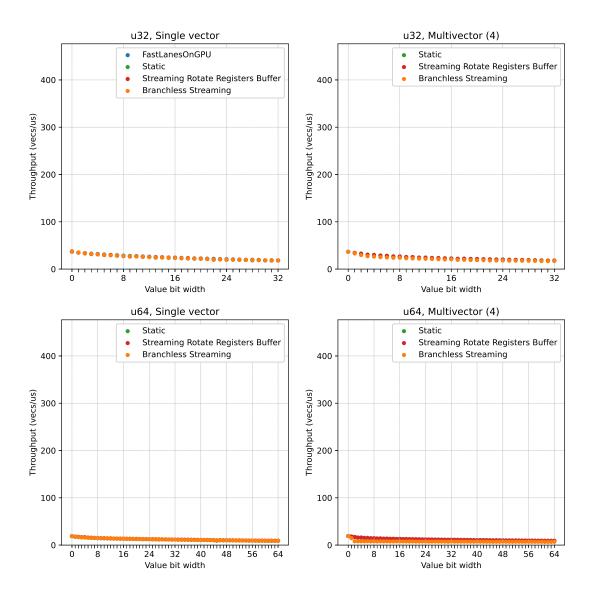

|              | 5.2                                                  | FFOR   | Microbenchmarks                                  | 41 |

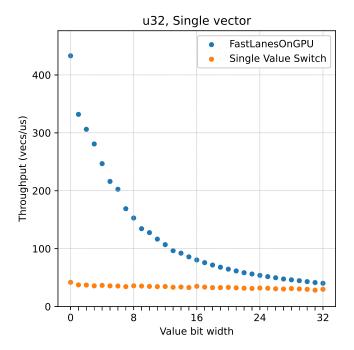

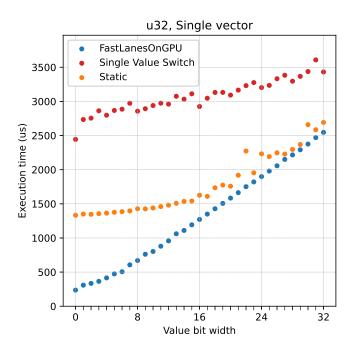

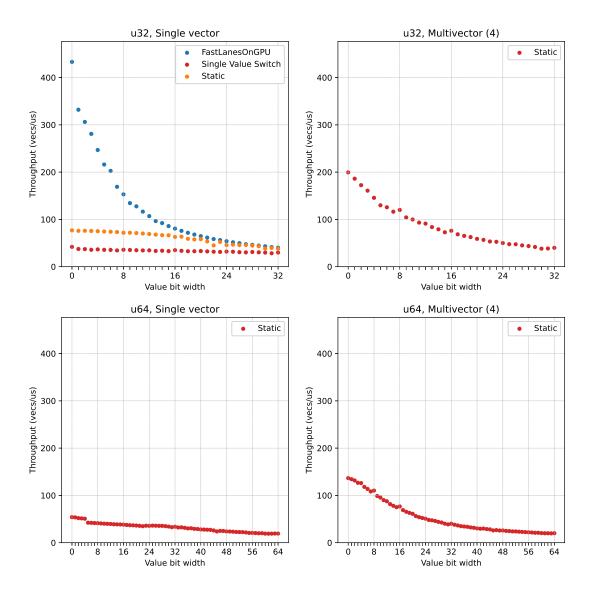

|              |                                                      | 5.2.1  | Switch Based Decoding                            | 42 |

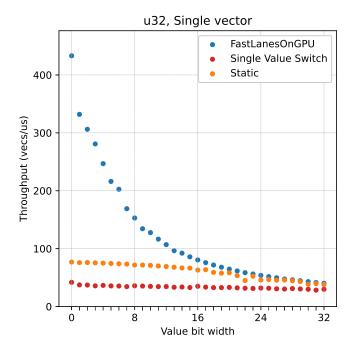

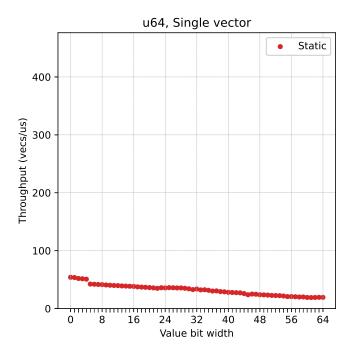

|              |                                                      | 5.2.2  | Static Decoding                                  | 43 |

|              |                                                      | 5.2.3  | Multi-Vector Decoding                            | 45 |

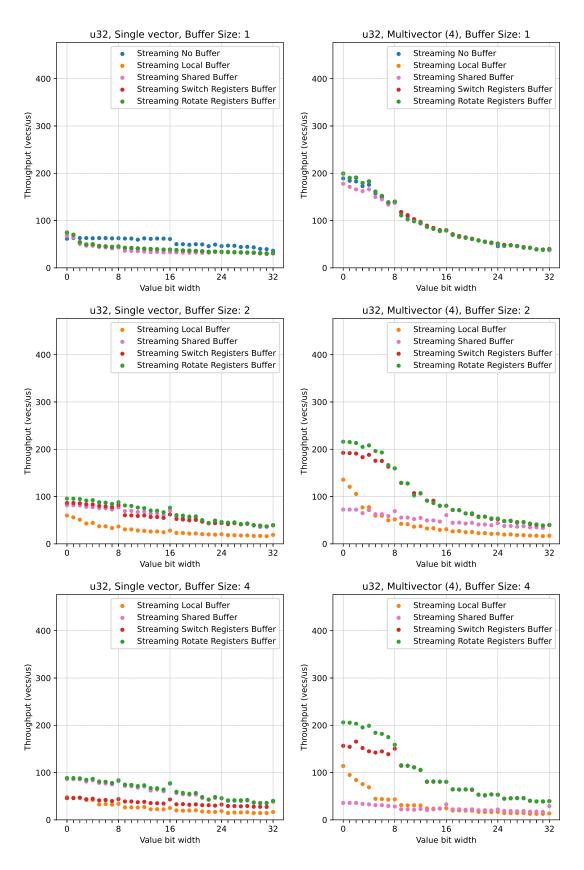

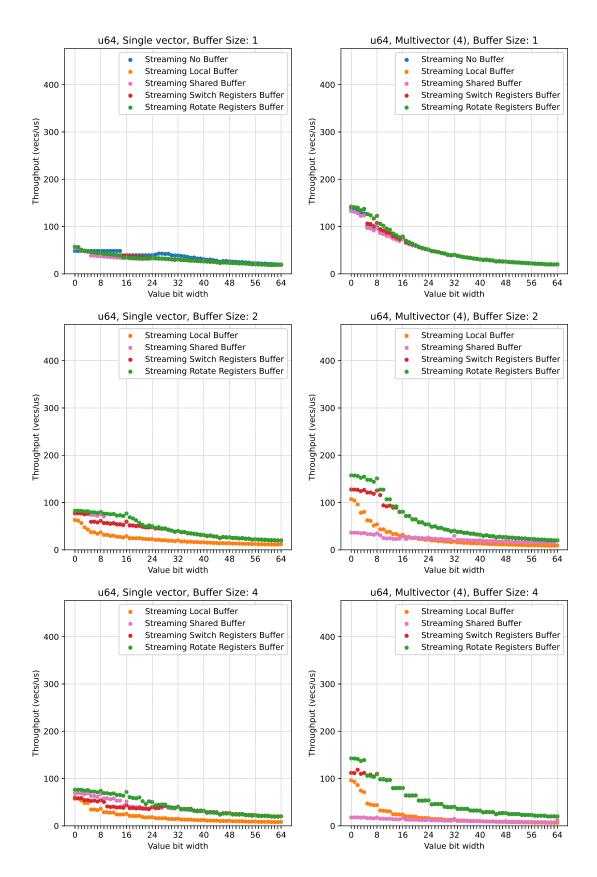

|              |                                                      | 5.2.4  | Streaming Decoding                               | 46 |

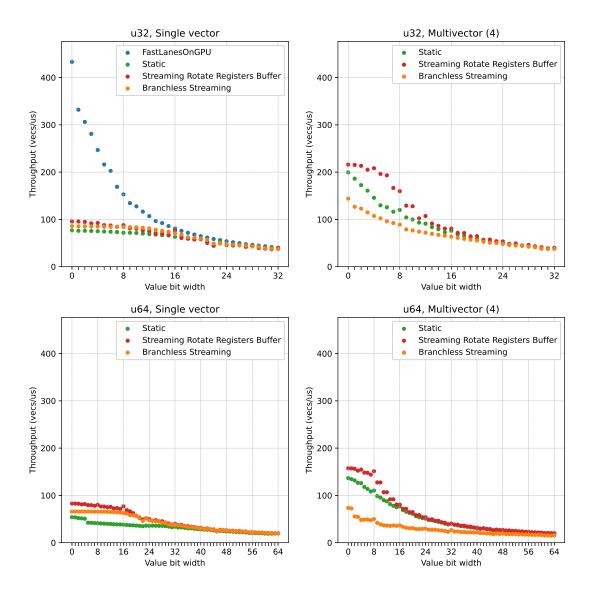

|              |                                                      | 5.2.5  | Branchless Decoding                              | 51 |

|              |                                                      | 5.2.6  | Full Decompression                               | 51 |

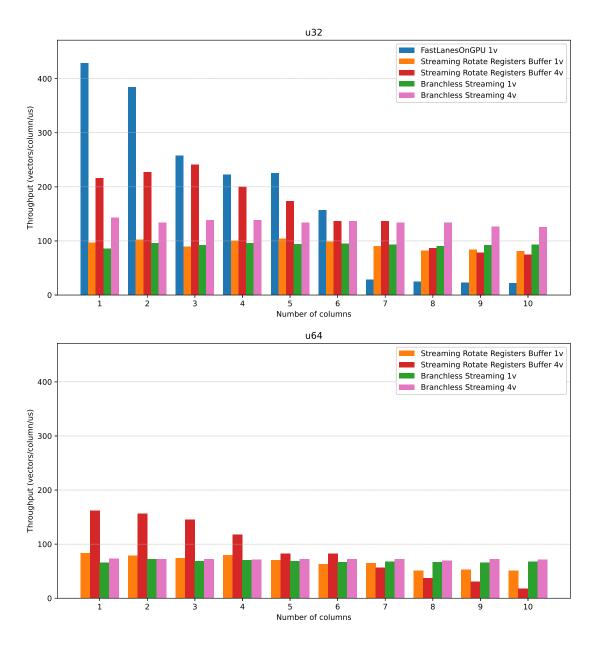

|              |                                                      | 5.2.7  | Multi-Column                                     | 56 |

|              |                                                      | 5.2.8  | Summary                                          | 56 |

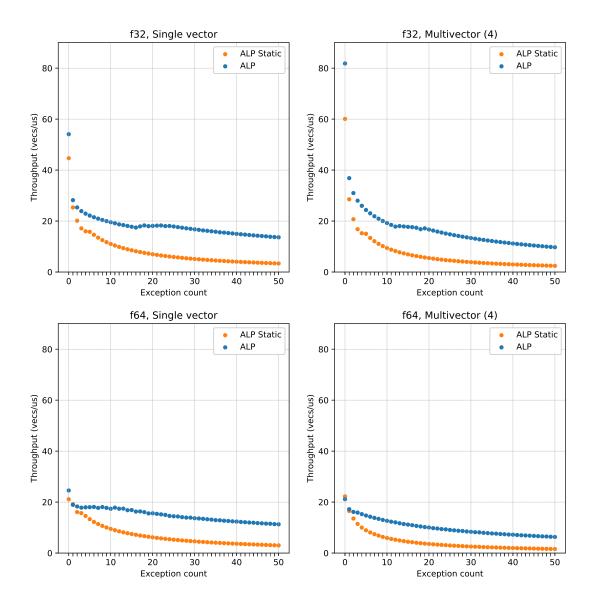

|              | 5.3                                                  | ALP N  | Microbenchmarks                                  | 57 |

|              |                                                      | 5.3.1  | ALP                                              | 57 |

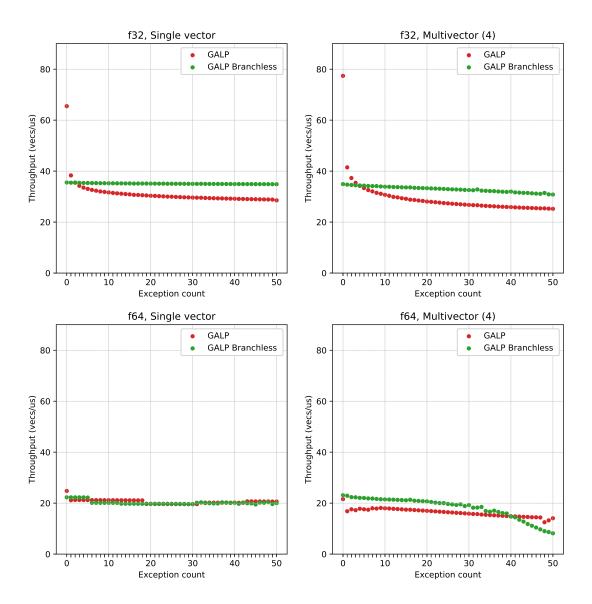

|              |                                                      | 5.3.2  | G-ALP                                            | 57 |

|              |                                                      | 5.3.3  | G-ALP With Buffering                             | 60 |

|              |                                                      | 5.3.4  | Multi-Column                                     | 60 |

|              |                                                      | 5.3.5  | Summary                                          | 64 |

|              | 5.4                                                  | Real I | Oata Benchmarks                                  | 64 |

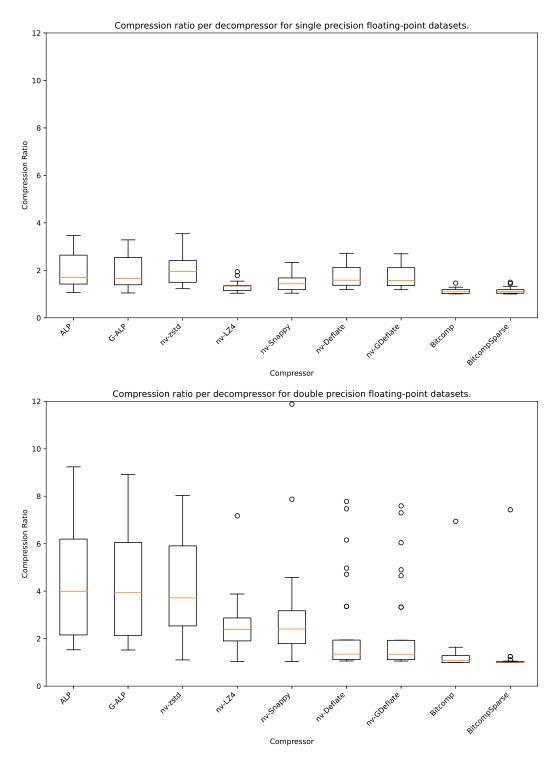

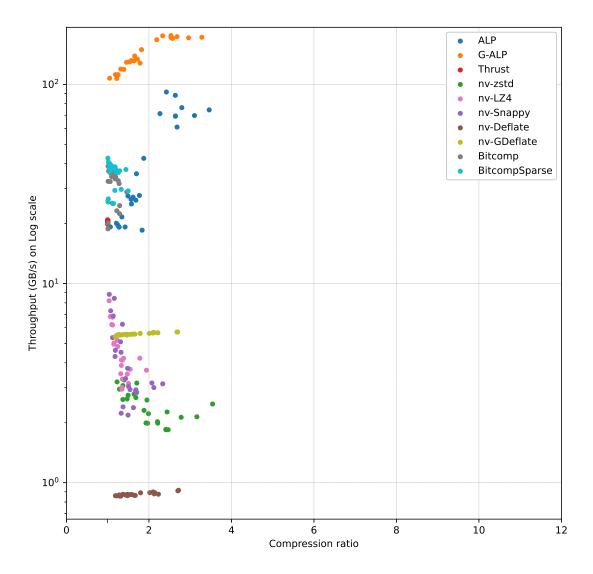

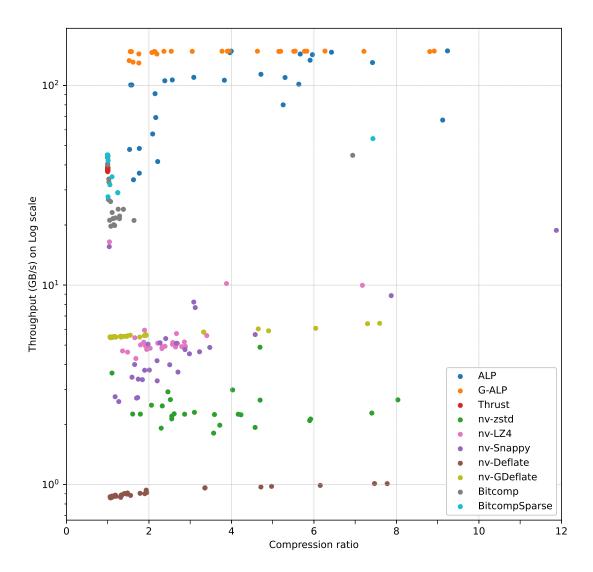

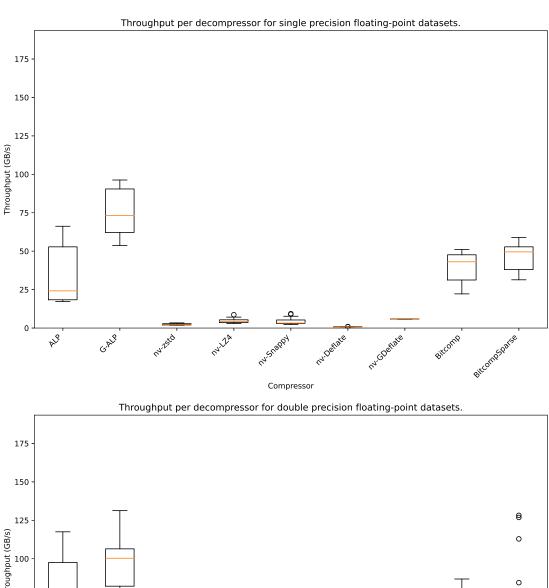

|              |                                                      | 5.4.1  | Compression Ratio                                | 66 |

|              |                                                      | 5.4.2  | Filter Throughput                                | 68 |

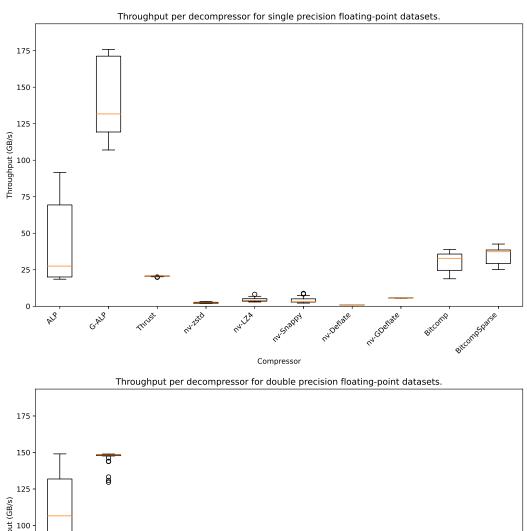

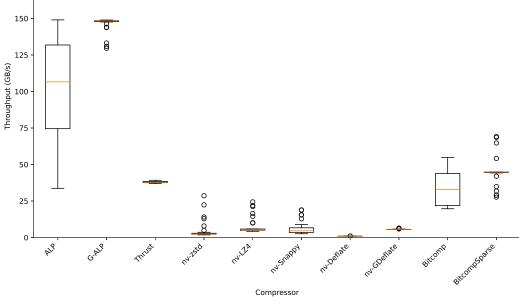

|              |                                                      | 5.4.3  | Full Decompression Throughput into Global Memory | 68 |

|              |                                                      | 5.4.4  | Summary                                          | 73 |

| 6            | Con                                                  | clusio | n                                                | 74 |

|              | 6.1                                                  | Resear | ch Questions                                     | 75 |

|              | 6.2                                                  | Future | e Work                                           | 77 |

|              |                                                      | 6.2.1  | CPU Benchmarks Data Parallel Exception           | 77 |

|              |                                                      | 6.2.2  | Benchmarking Other GPUs                          | 77 |

|              |                                                      | 6.2.3  | New Benchmarks                                   | 77 |

|              |                                                      | 6.2.4  | FastLanes GPU File Reader                        | 78 |

| A            | Benchmarking Environment 8                           |        |                                                  | 86 |

| В            | Single precision floating-point datasets results  8' |        |                                                  | 87 |

| $\mathbf{C}$ | Double precision floating-point datasets results 99  |        |                                                  | 93 |

#### Abstract

This thesis implements G-ALP, a data-parallel compression scheme for floating-point data that is suitable for decoding on GPUs. G-ALP expands upon ALP, which is part of the FastLanes file format encodings. The work in this thesis develops G-ALP by revisiting previous work on decoding FastLanes on GPUs, and by creating a new data-parallel exception layout. G-ALP is then compared with nvCOMP, a library of common compression schemes that were implemented for the GPU by NVIDIA. These comparisons are done on real-world datasets, for single-precision as well as doubleprecision floating-point data. G-ALP has one order of magnitude higher decompression throughput than other compressors, while achieving a compression ratio equal to that of the best competing compressor, zstd. Decoding throughput differences were even higher when data was not compressed into RAM but decoded directly within a data processing kernel. These results show that G-ALP is a viable encoding for compressing floating-point data on the GPU. Using G-ALP, floating-point data can be compressed, resulting in higher data transfer throughput from the CPU to the GPU, and can store more data in the GPU's RAM. With the fine-grained single value decoding API, the compressed data does not have to be decompressed into RAM, but can be read directly by a data processing kernel.

## Chapter 1

# Introduction

This thesis creates a decoder for decompressing floating-point data on *Graphics Processing Units* (GPUs). Compression has two benefits. The first benefit is that it is possible to store the same amount of information using less space. The second benefit is that it is then faster to transfer this information, as less physical data needs to be copied to transfer the same amount of information. Compression is interesting for GPU workloads, as information needs to be transferred from the host's RAM to the GPU using a PCIe link with relatively low throughput, and can also store more information in the GPU's RAM.

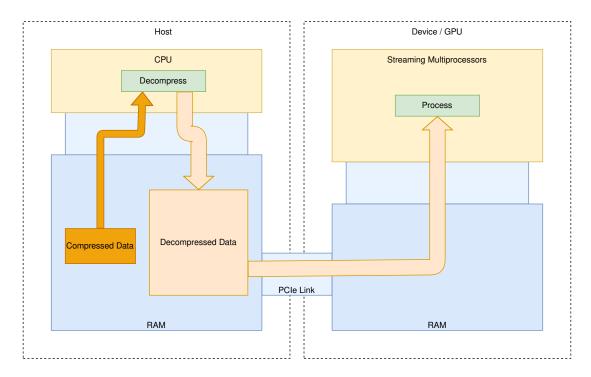

There are multiple possible scenarios for decompressing data before processing it on the GPU. In Figure 1.1 the most simple scenario is shown. The compressed data is decompressed on the CPU, before it is transferred to the GPU and processed there. The benefit of this approach is that it is simple, and can use common CPU decompressors. However, the GPU part of the workload does not benefit from compression, as the data is transferred in compressed form to the GPU, and stored in decompressed form on the GPU.

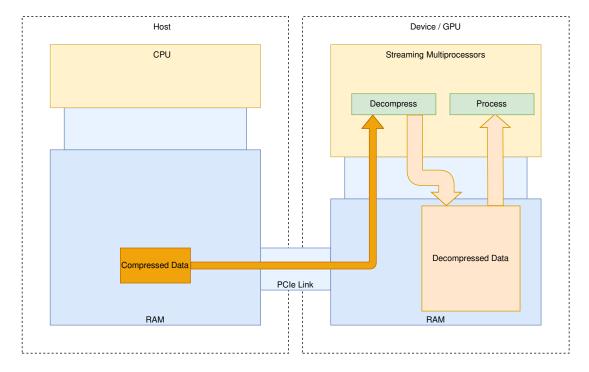

The second scenario is depicted in Figure 1.2, showing an alternative approach where compressed data is transferred to the GPU, and then decompressed into the GPU's RAM. This approach partially realizes the possible benefits of compression for GPU workloads. The data can be transferred in compressed form, however, the data still needs to be decompressed into the GPU's RAM, requiring a large allocation of memory.

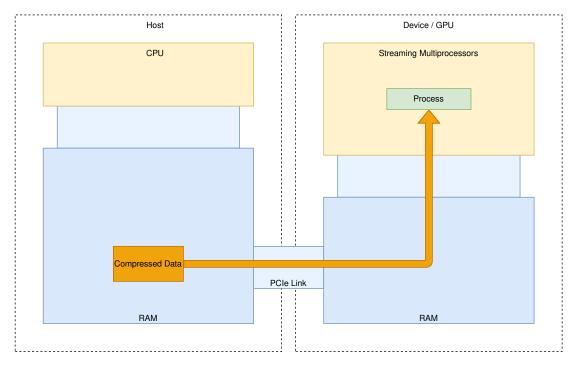

The third scenario in Figure 1.3 bypasses the decompression step completely. By using an API that gives GPU kernels fine-grained, high-throughput access to the data in compressed form, the data can be left compressed in RAM. This approach has the advantage of both benefits of compression. Data is never transferred in decompressed form, saving memory read throughput, and no memory is allocated for storing the decompressed data, saving RAM.

There are many GPU workloads that could benefit from compression. Any form of data processing where memory throughput is a bottleneck or RAM storage is a limit

Figure 1.1: First scenario of GPU processing of compressed data. The compressed data is first decompressed on the CPU, before being transferred in decompressed form over the relatively slow PCIe link. Decompressing the data before transferring the data over the PCIe link is slow, as the throughput of the PCIe link is limited.

could benefit. Such workloads could be AI training or inference workloads, data processing kernels or GPU databases. The second scenario in Figure 1.2 requires RAM to be allocated to store the fully decompressed data, but can be convenient in some cases, as kernels that process the data do not have to be changed and can simply load the data in non-compressed form. The third scenario in Figure 1.3 saves both memory transfer throughput and RAM, but requires kernels to be changed to use the fine-grained decompression API.

FastLanes[2] is a file format designed for big data online analytical processing (OLAP) workloads. In OLAP workloads, data is recorded and written once, and then read many times after that to analyze the data. With the FastLanes file format data can be compressed at ratios equal to those obtained by zstd[2, 11], and decompressed at high throughput using SIMD instructions. The central FastLanes bit-interleaved encoding can be efficiently decoded on GPUs, even speeding up certain memory-throughput-bound queries[4]. FastLanes has multiple encodings for different types of data. In previous work[4] one of the FastLanes encodings for integers was implemented for GPUs. FastLanes also has encodings for floating point data, one of which is ALP[5]. No Fast-Lanes encodings for floating-point data were implemented for GPUs yet. Therefore, this thesis implements a GPU decoder that efficiently decodes ALP encoded data with an unobtrusive API that offers fine-grained access to read compressed data.

Figure 1.2: Second scenario of GPU processing of compressed data. The data is transferred in compressed form over the PCIe link, then the data is decompressed on the GPU. The decompressed data is processed. This scenario is faster than the previous scenario, as the data is transferred over the PCIe link in compressed form. However, this scenario still requires a decompression kernel to be launched, and a large allocation of memory to decompress the data into.

Figure 1.3: Third scenario of GPU processing of compressed data. The data is transferred in compressed form over the PCIe link, and never decompressed into RAM. The processing kernel can use an unobtrusive API to access the data in compressed form, completely bypassing the decompression step. This approach does not have to allocate memory for the decompressed data, and can also load the data into the streaming multiprocessors in compressed form, saving memory read throughput.

Creating a decoder for decompressing floating-point data on GPUs consists of three parts. In previous work, one of the FastLanes encodings was successfully decoded on GPUs[4]. However, the decoding throughput of this decoder degraded when multiple columns were decoded concurrently. (1) Therefore the first part to implement is a new decoder that uses a new decoding approach with an API that should offer consistent high decoding throughput with a single value granularity, no matter how many columns are decoded simultaneously. To decode floating-point data on GPUs, an ALP GPU decoder should be implemented. (2) The second part of this thesis implements a decoding technique for high throughput exception patching for GPUs. Exception patching is an encoding technique to handle values that are outliers which are hard to compress separately from the majority of the values. ALP uses it to handle values which cannot be losslessly compressed using ALP's core compression method. (3) Finally, the third part of this thesis measures how performant ALP decoding on GPUs is. ALP decoding should be compared to the state of the art on GPU decompression, and NVIDIA implements a variety of common compression schemes in the nvCOMP library[42]. The GPU implementation of ALP's decoding throughput is compared to these nvCOMP compression schemes.

#### 1.1 Research Questions

The implementation and benchmarking of an ALP GPU decoder can be decomposed into three research questions:

RQ 1: How should a general purpose API for single value decoding of bit-packed data be implemented?

RQ 2: How can exceptions be efficiently patched on GPUs?

RQ 3: Can floating-point data be decoded faster with ALP than with common GPU compression schemes?

#### 1.2 Outline

This thesis first discusses the background of the research in Chapter 2. This background starts with a discussion of different kinds of compression approaches and their benefits. After that, the FastLanes file format[2] and ALP[5] are discussed. ALP is part of FastLanes and is a compression encoding for floating-point data. Finally, the nvCOMP library is discussed, nvCOMP is a compression library from NVIDIA that implements common compression schemes. Then in Chapter 3 NVIDIA GPU hardware internals are discussed. This chapter also provides an in-detail description of how programs are executed on GPUs.

Then the thesis continues in Chapter 4 with a discussion of how FastLanes encodings can be decoded efficiently on GPU. First multiple decoding approaches for the core FastLanes bitpacking encoding are discussed, and then multiple decoding approaches for patching exceptions in ALP are discussed. This chapter also designs G-ALP, which uses an alternative data-parallel exception layout to efficiently decode ALP encoded floating-point data on GPUs. In Chapter 5 the throughput of each decoder and exception patcher is extensively measured using microbenchmarks, and concludes with multiple benchmarks which compare the throughput and compression ratio of G-ALP with the compressors in the nvCOMP library on real-world data. Chapter 6, the final chapter, draws conclusions from the benchmarks, provides answers to the research questions and discusses future work.

## Chapter 2

# Background

This chapter explains why compression is useful on GPUs. First the benefits of compression are discussed, and what the advantages and disadvantages are of common compression schemes that rely on heavy-weight compression. Then the benefits of light-weight compression over heavy-weight compression are discussed. FastLanes is then introduced, FastLanes is a new data format that combines these light-weight compression benefits with data-parallel encodings that are ideal for processing with SIMD instructions. The chapter continues with a section that explains why compression is useful on GPUs, how it can speed up memory-throughput-bound kernels and why the FastLanes format is a good fit for data decompression on GPUs. Lastly, a brief explanation of NVIDIA's nvCOMP and Thrust libraries is given.

## 2.1 Compression

Encoding data into a format that uses fewer bits to store the same data is called compression. The original data can be retrieved by decoding the encoded data. Compression is useful for two reasons. The first reason is that less space is needed to store the same amount of data. Saving space can allow users of compression to store more data, or to use smaller storage devices to store that data. The second reason is that transporting encoded data is faster, as fewer bits need to be transferred to transfer the same amount of information.

Commonly heavy-weight compression (HWC) schemes are used to compress data. HWC can encode any kind of data, and are widely used in the industry. Examples of HWC are: zstd[11], Deflate[13], LZ4[10], and Snappy[17]. These schemes commonly rely on complex encodings such as Huffman coding[16] or LZ77[61]. Decoding these complex encodings requires many instructions, that are hard to parallelize. Heavy-weight compression schemes also operate on large blocks of data, requiring a relatively large amount of memory during decompression[1]. This high memory usage causes the decompression function to continuously spill data out of caches, introducing a memory

throughput bottleneck. Both the complex decoding and the high memory usage slows down the decoding of HWC significantly.

An alternative to HWC are *light-weight compression* (LWC) schemes. LWC operate on columnar data and rely on simple encodings. These simple encodings are faster to decompress, as decoding can be vectorized, requiring fewer and more parallel instructions, and little memory[62]. Using LWC can speed up database queries by leveraging the high decompression speed. The read throughput of data in kernels can then be increased by loading compressed data instead of normal data, and decompressing that data at the last moment before processing it[59, 15]. Some light-weight encodings are also directly interpretable in encoded form. This property enables databases to operate on those encodings without decoding the data at all.

An example of a LWC is *bit-packing*, a corner stone encoding upon which many other light-weight encodings expand. In binary representation, any integer in the range  $[0, 2^b)$  can be represented using b bits. However, on computers integers are represented as 8-bit, 16-bit, 32-bit, or 64-bit integers. If a set of integers is represented as 32-bit integers, but the set only contains values in the range  $[0, 2^b)$ , with b < 32, there are 32 - b bits that are always zero. Bit-packing compresses data by reusing these bits to store the bits of the next integer, instead of leaving those bits unused. A 32-bit integer can then contain two 16 bit values, or 16 two bit values. Smart bit-packing arrangements can even store bits of a single value across multiple integers, enabling for example three 32-bit integers to store four 24 bit values.

The FOR (Frame Of Reference) encoding expands upon bit-packing by preprocessing values before bitpacking those values[14]. Bitpacking can encode values that fit into a range  $[0, 2^b)$  with b bits. However, the smallest value within a range of numbers is not necessarily zero, so the lower bound of this range could be improved. A series of values might be encoded with fewer bits, by scanning a series of values and saving the smallest scanned value as the offset. The range of values  $[offset, 2^b)$  is then smaller if  $offset \neq 0$ . This smaller range can be mapped back to a range that starts with a 0 for bitpacking by subtracting the offset from each value. Then you get a new range  $[0, 2^{'b})$  that is smaller if b < b. The values can be decoded by unpacking the values, and adding the offset back to each value to retrieve the original values.

#### 2.2 FastLanes

FastLanes is a new next-generation big data format[2]. FastLanes is data-parallelized by utilizing the novel 1024-bit interleaved and Unified Transposed Layout[3], enabling fully parallel decoding even with scalar code on the CPU. Parallel encodings are faster to decompress as there are no dependencies between instructions, and parallel encodings can leverage SIMD instructions for high-throughput decoding of data. FastLanes significantly outperforms the state-of-the-art, achieving an 80× speedup on the M1 processor

compared to Parquet, an industry standard data format, while also achieving a 40% better compression ratio.

FastLanes uses the concept of vectors to group values within columns, based on the work of Zukowski  $et\ al.[7]$ . Vectors are groups of 1024 values that are compressed with the same parameters. By grouping values together this way, there are many costs that can be amortized across 1024 values instead of incurring them for decoding every value. Vectorization of data decoding also exposes more parallel instructions to the compiler, which can be executed faster in pipeline based processors. When using bitpacking as a compression method, the range of all values of a vector of 1024 values decides with how many bits each value in the vector will be packed using the 1024-bit interleaved layout. The FFOR (FastLanes Frame Of Reference) encoding is based on the bitpacking mechanism and contains an offset per vector of values. During decoding, the offset addition is fused with the SIMD instructions for unpacking the values, to be able to keep the data in the SIMD registers.

Exception patching is a technique to even further increase the possible compression ratio, while retaining high throughput decoding performance [62]. If for example an FFOR vector contains a single outlier, the range of values in that vector is significantly increased, requiring all values to be packed using more bits. Instead, by using exception patching, that outlier can be marked as an exception, and separately encoded. Then the FFOR range can be calculated using the range of all non-outlier values. During decoding, packed values that are actually exceptions can be replaced with the value of the exception.

In the FastLanes file format, these different light-weight encodings such as FFOR and exception patching can be combined and cascaded using the Expression Encoding feature of FastLanes. FastLanes defines a set of *encoding operators*[2] and, by using Expression Encoding, each column can be encoded by combining a series of these operators into an *encoding expression*. By combining these LWC expressions, compression ratios equal to HWC schemes such as zstd can be achieved[6].

FastLanes also has an encoding to encode floating-point data, called Adaptive Loss-less floating-Point Compression (ALP)[5]. As the name implies, the encoding can loss-lessly compress both single-precision as well as double-precision floating-point data. The encoding expands upon PseudoDecimals[20]. PseudoDecimals observed that floating-point data in real datasets are commonly storing data that each could also be represented by storing an integer in combination with an exponent e. An example of this kind of data is monetary data, which has a limited, and fixed number of decimals. This is important, as the binary representation of floating-point data is not suitable for LWC such as FOR. The data can be compressed better by mapping floating-point data to these integers and exponents, as these integers can then be compressed using run-length encoding and FOR.

ALP improves upon PseudoDecimals in compression speed, decompression speed and

compression ratio [5]. (De-)Compression speed is improved by vectorizing the encoding and decoding, using primitives from the FastLanes compression library. Compression ratio is improved by defining an exponent per vector of values, instead of per individual value. This amortizes the storage cost of the exponent across 1024 values instead of a single value. Additionally, ALP uses an additional multiplication with a factor f to cut off trailing zeros from the integer part of the representation. This is mostly useful when the exponent is comparatively high, causing the resulting integer to contain many trailing zeros.

However, approximately one percent of decimal values cannot be mapped to exact double-precision values using a combination of an integer and exponent. These values are separated from the other values, and handled with the exception patching mechanism. To decode the data, first the bit-packed integers are decoded, and then mapped back to floating-point data. The values that could not be mapped to integers are then replaced with the original values. In cases where most of the floating-point values in a column cannot be represented as a pair of integer and exponent, ALP uses an alternative encoding called ALPrd. ALPrd refers to these values as *real doubles*, as they do not originate from data that could be stored as decimals with fixed precision. ALPrd is not implemented in this thesis.

## 2.3 Compression on GPUs

Compressing data can be promising for GPUs, as all data needs to be transferred via a comparatively slow PCIe link between the GPU's RAM and the CPU's RAM. Compressing data alleviates the problem of a slow PCIe link, because compressed data takes less time to transfer than non-compressed data, as less data needs to be moved. Additionally, more data can be fit into the GPU's RAM by compressing the data.

Shanbahg et al. [56] pioneered the idea of leaving the data compressed in the GPU's RAM. This ensures that no memory needs to be allocated in the GPU for the decompressed data, allowing one to store more data on the GPU. Shanbahg et al. use a cascaded compression scheme, where the compressed data needs to be read multiple times before the data is fully decompressed. To avoid reading data multiple times from RAM and further increasing pressure on the RAM throughput bottleneck, they store the compressed data in the GPU's shared memory. They then decompress that data during the execution of a query. They adopt the notion of a tile of data, which is similar to the concept of a vector of data. A tile is a fixed size group of values that fits in the GPU's shared memory.

This approach of loading compressed data has an additional benefit besides being able to store more data in the GPUs RAM. Loading compressed data from RAM into registers is faster than loading non-compressed data, as fewer bytes need to be loaded to transfer the same amount of data. However, the overhead of decompressing the

tile-based encoding was too large to make use of this transfer benefit.

The bitpacking encoding from FastLanes was also implemented for GPUs[4]. The data-parallel encodings that work well with SIMD instructions also fit the warp-based execution model of GPUs very well. This initial implementation showed that the data-parallel FastLanes encoding makes the decompression overhead much smaller. Because the decompression overhead is smaller, the kernels can leverage the benefit of loading compressed data, and the memory-throughput-bound kernels can actually be faster by loading compressed data. The initial GPU API uses the vectorized execution model—the most widely adopted execution model on the CPU. However, on GPUs this forces kernels to materialize 32 values per thread per column. On GPUs the amount of high-throughput, nearby memory (registers, shared memory, L1 cache) per thread is limited, and materializing 32 values per thread negatively affects occupancy, as will be further explained in Section 3.5.

#### 2.4 nvCOMP

NVIDIA's nvCOMP compression framework [42, 39, 46, 53, 23, 30] offers multiple compression schemes to compress and decompress data on the CPU as well as the GPU. The framework is widely used, with more than 608,509 downloads [40]. nvCOMP compression encodings supports multiple data types: bytes, multiple integer types, strings, and half precision floats [38]. nvCOMP contains no direct compression methods for single precision or double precision floats, instead this data can be compressed as a stream of bytes. nvCOMP consists of several heavyweight compression schemes such as LZ4, Snappy, ZSTD, and Deflate, as well as GPU-optimized formats like Bitcomp (proprietary and closed-source) and GDeflate.

GDeflate is a GPU-friendly variant of Deflate that introduces interleaved Huffman coding, where codes are permuted into 32 partitions, though its details are vaguely explained[30]. This enables intra-threadblock parallelism, allowing GPU threads within a block to decode different partitions simultaneously, similar to interleaved bit-packing in FastLanes, where data is distributed across 32 lanes. For LZ4, nvCOMP enhances its GPU-friendliness by breaking datasets into blocks and compressing/decompressing each block using a thread block[46]. Within each thread block, only a single warp is used to ensure efficient coordination among threads via warp-level primitives.

CUDA, NVIDIA's programming language for GPUs, requires programmers to manually control when data, and which data, is copied to and from the GPU. There is no spilling mechanism that automatically spills memory to the CPU's RAM if the GPU's RAM is fully used. This lack of spilling poses a problem for heavy-weight compression schemes with arbitrary block sizes, if the format does not contain metadata on the decompressed size for each block. Because otherwise during decompression the program might segfault if there is no more memory to write the contents of the decompressed

block to. nvCOMP extends every compression method that they support with an additional header that contains decompressed block sizes. nvCOMP can also decompress data that does not contain this NVIDIA specific header, but then it will either allocate the maximum needed memory to decompress a block if that size is known, or nvCOMP will do an expensive preliminary pass first to calculate how much memory the decompressed data will need[37].

# Chapter 3

# NVIDIA Graphics Processing Units

This chapter explains what graphics processing units (GPUs) are, how they execute programs and how they differ from central processing units (CPUs). First the general execution model of GPUs is discussed, which introduces most related terminology regarding GPUs. After that the memory hierarchy of GPUs is discussed. Then warps, the smallest computational unit of GPUs, are discussed. Then there is a section on streaming multiprocessors and a section on occupancy. The chapter concludes with two microbenchmarks. The first microbenchmark highlights how the multi-pipeline architecture of GPUs influence execution time. The second microbenchmark shows that improving instruction-level-parallelism (ILP) increases the throughput of a memory latency bound kernel, using a variant of a pointer chasing benchmark.

This thesis only benchmarks, and refers to, NVIDIA GPUs, not GPUs from other manufacturers. This choice was made as most literature on GPUs uses NVIDIA GPUs, and NVIDIA GPUs dominate in the industry as well.

Generally, the exact hardware of NVIDIA GPUs is not officially documented. The official documentation only consists of white papers and sales information, both of which often lack detail and complete benchmarks. Instead there are a number of papers which perform microbenchmarks to dissect a specific architecture of NVIDIA GPUs, such as the Volta[19], Turing[18] and Hopper[22] architectures.

#### 3.1 Execution model

GPUs excel in executing highly parallel programs, where the program needs to repeatedly execute the same computation on a large set of data. Developers can program GPUs by writing CUDA, which is essentially C++ with extra keywords. C++ functions can be configured to run on the GPU by simply writing the \_\_global\_\_ keyword in front of the function signature. This indicates that this function will be called from the

host (CPU) and run on the device (GPU). These functions are written as if a single thread is independently executing the code.

Threads are grouped into thread blocks, which consist of up to 1024 threads. Thread blocks are in turn grouped into grids. When calling a  $\_\_global\_\_$  function, one needs to specify the grid and thread block configuration that will execute that function. For example, when adding two vectors, vector A and vector B, that each contain 102400 elements, one could launch a grid of 100 thread blocks, each thread block containing 1024 threads. In that function thread i would add A[i] and B[i] together and store the result at index i in the output vector C. Listing 1 shows a minimal example of CUDA code that executes this vector addition.

```

1 // GPU Function

2 __global__

3 void sum_vectors(const int *A, const int *B,

int* C, const size_t size) {

// Calculate index of thread by reading special CUDA variables

5

int thread_id = blockDim.x * blockIdx.x + threadIdx.x;

6

if (thread_id < size) {</pre>

C[thread_id] = A[thread_id] + B[thread_id];

9

}

10

11 }

13 // CPU Function that uses the GPU to execute the sum.

14 // The d_ prefix hint that these ptrs point to device memory

void sum_vectors(const int *d_A, const int *d_B,

int* d_C, const size_t size) {

16

const size_t block_size = 1024;

17

const size_t grid_size = size / block_size + 1;

18

19

// The <<<int, int>>> is used to configure

20

// the thread grid and thread block

21

sum_vectors<<<grid_size, block_size>>>(d_A, d_B, d_C, size);

22

23 }

```

Listing 1: This code is a minimal example of how programmers can program a vector addition kernel in CUDA.

However, threads are an abstraction over how GPUs actually execute programs. The GPU differs from a CPU in that it does not contain a unique processing instruction pipeline for each individual thread. Instead GPUs contain *streaming multiprocessors* (SMs), which execute multiple thread blocks concurrently. Each SM consists of *warps*. An overview of the GPU internals is given in Figure 3.1. The SM distributes the threads of a thread block among these warps, where each warp is assigned 32 threads. All of the threads within a warp step through the same instruction for the program that they are

Figure 3.1: Diagram of the internal hardware of the GPU, and how the GPU (device) is connected to the host. Streaming Multiprocessors (SM) consist of multiple Processing Blocks (PB), the exact number of processing blocks varies per SM generation. Blue: Memory units. Yellow: Compute units.

executing. NVIDIA calls this the single instruction, multiple threads (SIMT) model[50].

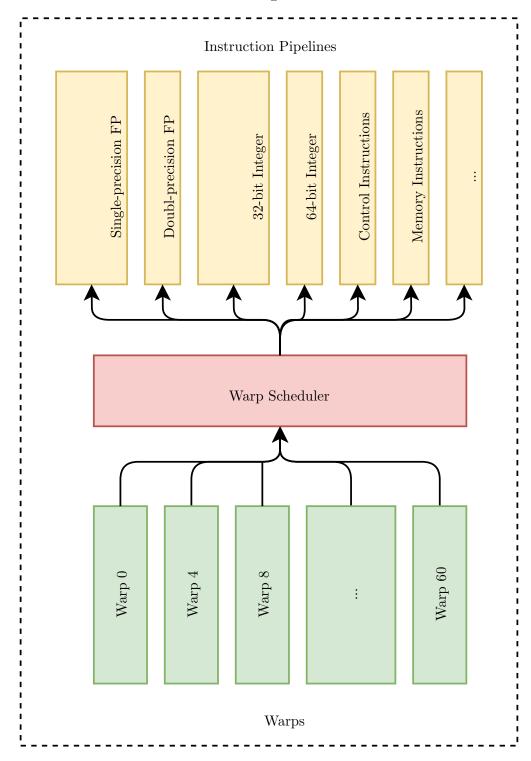

The warp itself does not actually execute any instructions, the warp only issues instructions[34]. When a warp issues an instruction, the instruction is passed to a separate instruction pipeline which will execute that instruction. There are multiple heterogeneous instruction pipelines in the SM, where each type of pipeline executes only a specific set of instructions. The warps within a SM are divided into groups, processing blocks, which share a set of these instruction pipelines[44]. A diagram of a processing block is shown in Figure 3.2.

Each processing block has a warp scheduler, which at every cycle 'picks' a warp that may issue an instruction to the instruction pipelines within that processing block. Warps might not be able to issue an instruction if they encounter a data hazard or a control hazard, then they need to wait for a previous instruction to finish. This can effectively hide the latency of the instruction that the warp is waiting on, because the warp scheduler can then choose to execute the instructions of other warps[35].

## 3.2 Memory

The main memory hierarchy of a GPU consists of an L1 cache, an L2 cache and the device's RAM. Each SM has it's own L1 cache, The L2 cache is shared among all SMs. Global and local memory are logical subdivision of main memory that use the L1 cache conventionally. Additionally, a GPU has three other variants of memory that have a different version of the first level cache: constant memory, texture memory and shared memory. On some GPUs these memories are all still physically located on the L1 cache, and then the L1 cache is referred to as the *unified cache*.

Global memory is the term for regular memory, and is the most common form of memory. The memory resides in the GPU's RAM until it is read, then it is placed in the L1 cache, until it gets evicted into the L2 cache. Global memory accesses that are not cached have high latency and low throughput. For optimal read performance, global memory accesses need to be coalesced. Otherwise a single read transaction will result in loading multiple cache lines to fetch all necessary data[32].

Local memory functions the same as global memory, but the compiler chooses what memory is stored in local memory. The compiler will use local memory to store very large arrays, to store arrays that are dynamically accessed, to pass arguments to device functions that were not inlined, and to spill registers[29]. Because local memory functions the same as global memory, it has higher latency and lower throughput than reading from registers. Therefore it is necessary to be conscious about if a kernel uses local memory, and whether it is possible to avoid using local memory.

Local memory is used when calling functions that were not inlined. The compiler needs to store the state of the registers before entering the non-inlined function into local memory. Then when the function finishes the register state needs to be restored.

Figure 3.2: Layout of a processing block within a SM. Each cycle, the warp scheduler picks one warp to take an instruction from, and sends that instruction to one of the appropriate instruction pipelines. In this example the first of four processing blocks is depicted, with twice as many single precision as double precision instruction pipelines. Warps are evenly distributed among all processing blocks within a SM, where the function  $warp\_index$  mod  $total\_processing\_blocks = block\_index$  decides to which processing block a warp belongs[19]. The number 7 processing blocks per SM can differ per compute capability, typically between two and four processing blocks per SM. Yellow: Instruction Pipelines. Red: Warp Scheduler. Green: Warps.

This is relatively slow and increase the load on the already scarce L1 cache memory read throughput. To avoid this problem, the NVIDIA compiler tries to aggressively inline functions.

Constant memory and texture memory are both read-only for code running on the GPU. The constant cache is relatively small, and is optimal when all threads within a warp need to access the same value[51]. If the value is not cached in the constant cache, it is loaded from the GPUs RAM. The texture cache is optimized for repeated 2D array accesses with spatial locality[29].

Shared memory is addressed by memory banks, which enables warps to do uncoalesced access without a performance penalty, conditional on that there are no bank conflicts. Bank conflicts occur when two threads read different memory addresses that are located in the same memory bank. Shared memory allocated to a block can be read from, and written to, at runtime by all threads within that block. This means it is possible to use shared memory for inter-thread communication [54]. Loading data from global memory to shared memory requires the memory to first be loaded into the registers. However there exists a direct copy PTX instruction[47] on compute capability 8.0 and newer, which can be called with inline PTX[28].

Registers represent the fastest form of memory, and the number of registers per thread is dynamic, with a maximum of 255 registers per thread[51]. Registers have the lowest latency and highest throughput of all memory types. Registers are actually not located in the warp themselves, but in the register bank of the SM. However, registers are cached within the warp itself. The warp can cache four registers for each thread. This register caching can help prevent register bank conflicts, although studying these conflicts requires manual inspection and adjustment of the SASS assembly, so it is in most cases not a feasible optimization[19].

The GPUs assembly not only contains normal load instructions, but also vectorized load instructions. Instead of loading a single value per thread per instruction, the vectorized load instructions fetches four consecutive values per thread per instruction. The vectorized load instructions therefore can fetch more memory per instruction. This enables the SM to use fewer load instructions to fully saturate the memory bandwidth. The vectorized load instructions are particularly useful on architectures with relatively low memory instruction throughput [26].

In CUDA the developer manually controls which memory is copied to and from the GPU over the PCIe link, there is no mechanism that can spill memory from the GPU's RAM to the CPU's RAM or to disk.

## 3.3 Warps

CUDA enables developers to program the GPU as if they were programming a single, independent thread. However, on the hardware side the smallest unit of computation

is not the thread, but the warp. Programming those warps as if they only execute a single thread can leave a lot of performance on the table. It is better to think of GPU instructions as vector instructions[58].

Warp divergence occurs when not all threads within the same warp take the same branch within the program [24]. In that case, the warp will execute both branches sequentially. The threads that do not enter the branch are disabled. At run-time the program can query which threads within the warp are disabled by querying the value of the  $active\ mask[52]$ .

When issueing memory accesses to global memory, each thread can access an individual value. However, if threads access values that are aligned on the same 128-byte cache line, the warp will *coalesce* these memory accesses. This means that instead of fetching the same 128-byte cache line multiple times, it will only fetch this line once, and give each thread it's own requested part of the line. Coalescing is only applied to memory accesses of threads in the same warp, so memory accesses from different warps cannot be coalesced[32].

This coalescing is also the reason why sequential memory access is faster on GPUs than random memory accesses. Sequential memory accesses result in fully coalesced memory accesses, while random memory accesses will need to fetch a different 128-byte cache line from RAM for each thread in the warp, resulting in a 32x decrease in effective memory throughput. As each thread only needs part of the 128-byte cache line, but pays the cost in throughput for fetching the entire line.

## 3.4 Compute capability

The compute capability of a GPU indicates what the version is of the SMs in the GPU. Each compute capability can differ from previous ones, changing how much compute throughput, how large the cache sizes are, or changing other properties of a SM. Multiple GPUs can share the same compute capability. These GPUs then differ in other aspects, such as the number of SMs per GPU, the amount of RAM, the type of memory link, etc. The properties of each compute capability can be found in NVIDIA's documentation[25], as well as the compute capability of every NVIDIA GPU[55].

In Table 3.1 the memory and occupancy properties of a selection of compute capabilities can be seen. The selected compute capabilities are 6.1, 7.0, 8.9 and 9.0. Compute capability 6.1 is shown as it is the compute capability of the GPU on which all development for this thesis was done. Compute capability 7.0 is the compute capability of the V100 GPU. The 8.9 compute capability is a compute capability optimized for visual computing, used predominantly in consumer cards, and the development GPU of CWI has this compute capability. Compute capability 9.0 is the most recent datacenter GPU compute capability.

Several of the properties of the compute capabilities are identical. The total number

| Compute capability       | 6.1 (GTX 1060) | 7.0 (V100) | 8.9 (RTX 4070) | 9.0 (H100) |

|--------------------------|----------------|------------|----------------|------------|

| Max threads per block    | 1024           | 1024       | 1024           | 1024       |

| Resident threads         | 2048           | 2048       | 1536           | 2048       |

| Resident warps           | 64             | 64         | 48             | 64         |

| Resident blocks          | 32             | 32         | 24             | 32         |

| 32-bit registers         | 65536          | 65536      | 65536          | 65536      |

| Max registers per thread | 255            | 255        | 255            | 255        |

| L1 Cache (kb)            | 48             | 128        | 128            | 256        |

| Shared memory (kb)       | 96             | 96         | 100            | 228        |

Table 3.1: The resources available per SM for four different compute capabilities. Note that the total number of registers per SM stays constant, while the L1 cache and shared memory cache increases. The number of threads per SM is also the same for each SM, except the RTX 4070, which is a consumer GPU, optimized for visual compute.

| Compute capability            | 6.1 (GTX 1060) | 7.0 (V100) | 8.9 (RTX 4070) | 9.0 (H100) |

|-------------------------------|----------------|------------|----------------|------------|

| Registers                     | 32             | 32         | 42.7           | 32         |

| L1 Cache (bytes)              | 24             | 64         | 85.3           | 128        |

| L1 Cache (4 byte values)      | 6              | 16         | 21.3           | 32         |

| Shared memory (bytes)         | 48             | 48         | 66.7           | 114        |

| Shared memory (4 byte values) | 12             | 12         | 16.7           | 28.5       |

Table 3.2: On-chip memory resources per thread at 100% occupancy. The number of registers per thread at 100% occupancy is equal for all SMs, except the RTX 4070, which was optimized for visual compute. Each thread has access to very little L1 cache space at 100% occupancy, only able to store 32 integers or 16 long integers on average with the latest SM.

of registers is the same, as well as the maximum number of registers that can be assigned to a thread, and the maximum number of threads that can be assigned to a single block.

All of the compute capabilities also have a maximum number of resident threads, warps and blocks. This means that there cannot be more threads, warps or blocks active than that maximum. This has important implications for the block sizes of kernels. Because all compute capabilities have twice the number of resident warps the number of resident blocks, a thread block should always consist of at least two warps. Otherwise the bottleneck is the maximum number of active blocks instead of active warps.

The compute capabilities that specialize in visual computing differ by having only 1536 maximum threads per SM, and also a reduced number of resident warps and blocks. Because other properties such as the total number of registers does not decrease for these cards, there are more registers available per thread.

Table 3.2 shows the available on-chip memory per thread. In comparison to CPUs the number of registers and the L1 cache of SMs is relatively large, but when sharing those resources among all threads, the on-chip memory resources are very scarce. A single thread can only have a resident set of up to 32 integers or single-precision floats in the

L1 cache. This effect is aggravated when considering that L1 cache lines on NVIDIA GPUs are 128 bytes wide[32], so when all threads access values that are on unique cache lines, the number of values that can be cached is further reduced. So a GPU thread can only have 32 values cached in the L1 cache under optimal circumstances, whereas CPU threads commonly can store KBs of data in the L1 cache.

#### 3.5 Occupancy

The occupancy of a kernel is the ratio of active warps to the maximum total number of warps for a specific kernel [45]. High register usage, high shared memory usage, or low threadcount per block can decrease the occupancy for a specific kernel.

High occupancy indicates that there are many warps active on the SM. Having many warps active concurrently allows the GPU to hide latency better. While some warps are waiting on instructions with a long latency, other warps can issue instructions to make use of the SM's resources. This can hide the latency of instructions, as the SMs resources were still fully saturated while waiting for instructions with higher latency. So high occupancy increases the number of active warps, and therefore increase the chance that there are warps that can issue an instruction while other warps are stalled.

High register pressure means that the kernel uses many registers per thread. As the total amount of registers per SM is fixed, the SM will not activate every warp, thus decreasing the occupancy. By not activating every warp, the warps that are activated can still be assigned enough registers [49].

The exact maximum occupancy due to register usage is best calculated by using NVIDIA's Occupancy Calculator [45], as there are multiple factors that influence the occupancy for a certain number of used registers per thread. Registers cannot be allocated to a block in increments of one, neither are register allocated to a single thread, but only to a warp as a whole. Saving a single register can have a large effect on maximum occupancy, as it might allow the block to save a new allocation of a large number of registers. But saving a single register can also have no impact, if there is no lower threshold of allocated registers in reach.

High shared memory usage is also problematic for occupancy, as there also needs to be enough shared memory for all active blocks. Allocating all of the available shared memory to a single block will ensure that no other block of that kernel can run concurrently on the same SM. This limitation can however be leveraged in microbenchmarks to test the performance of a single thread in isolation[58], by allocating the maximum shared memory to a single block consisting of a single thread.

As mentioned in Section 3.4, allocating less than two warps per block can also decrease occupancy, as the number of maximum resident warps is at least twice as large than the maximum number of resident blocks. Any block using less than two warps will therefore suffer a decrease in occupancy.

Registers and shared memory are allocated to a block, until the last thread of that block finishes [27]. This is important, as any thread that is an outlier in regard to execution time will ensure that the resources of the entire block cannot be released until that thread finishes. So it is also possible that the occupancy is decreased by having a single long running thread, as the next block cannot be scheduled until that thread finishes.

#### 3.6 Assembly

CUDA code is compiled by nvcc[41] to PTX[47], which is in turn compiled to SASS, which has a listed, but undocumented instruction set[43]. PTX is an intermediary language which ensures that every binary can run on every NVIDIA GPU. Each generation of SM can have different assembly instructions. SASS is the actual assembly language that is compiled to the machine code which runs on the GPU[48].

The most important note about the SASS instruction set is that, unlike the PTX instruction set[47], there is no actual division instruction. Instead, the PTX division instruction is translated into approximately forty SASS instructions that actually executes the division<sup>1</sup>. Other optimizations, such as inlining, are also not yet applied in the PTX<sup>2</sup> binary. This means that evaluating PTX is not particularly useful for any performance insights, instead it is more beneficial to study the SASS that is generated from that PTX.

The actual machine code generated from SASS differs in some aspects from architecture to architecture. Details about the machine code were uncovered by academic papers[18, 60]. Since the Kepler architecture, the machine code consists of two parts: the instruction itself, and the control logic. The control logic is read by the warp scheduler, and controls how warps are picked to issue instructions. There are a multitude of open source assemblers created by third parties in order to be able to manipulate the machine code by manually writing SASS code<sup>3,4,5,6,7</sup>, as the NVIDIA provided toolchain does not offer an option to do this. Although these open source assemblers are unmaintained or archived, and only target a specific architecture, a developer can still study the source code to learn more about generating NVIDIA GPU machine code. There is also a utility available that can retrieve hardcoded instruction latencies from the NVIDIA assembler<sup>8</sup>.

GPUs contain no branch predictor, and a warp issuing a branch instruction will simply stall[31]. There is currently also no out-of-order execution on GPUs[8]. Branching

```

1https://godbolt.org/z/q6GaWf6Ef

2https://godbolt.org/z/1WW7Whazx

3https://github.com/cloudcores/CuAssembler

4https://github.com/NervanaSystems/maxas/

5https://github.com/hyqneuron/asfermi

6https://github.com/daadaada/turingas

7https://github.com/laanwj/decuda

```

in GPU code therefore has different performance characteristics than branching in CPU code. Stalling is not necessarily negative, as another warp can then issue instructions if there is a warp waiting.

## 3.7 Microbenchmark: Heterogeneous Instruction Pipelines

As explained earlier, warps only issue instructions. These instruction are then executed on a heterogeneous set of instruction pipelines. Each instruction pipeline only executes a specific set of instructions. There are different instruction pipelines for memory instructions, single precision arithmetic, double precision arithmetic, control flow and more. Each compute capability can have different types of instruction pipelines, and can have different ratios of throughput per type[25]. The execution time of a kernel can be improved by changing it's instruction mix. If a specific type of instruction pipeline is currently the bottleneck, part of the kernel could be changed to use less instructions of that bottleneck type, in exchange for more instructions that are executed on a less used type of instruction pipeline.

To prove that changing the type of instructions works, we benchmark the execution times of two different functions. One function exclusively executes arithmetic instructions, and the other function uses mainly memory instructions in exchange for fewer arithmetic instructions. What these functions actually do is irrelevant, as long as they issue different kinds of instructions, and most importantly take approximately the same amount of time to execute. In a real world scenario one could equate this to two different implementations of the same function, where microbenchmarks show neither implementation to actually perform better than the other.

```

template<typename T>

__device__ T arithmetic(T value, const T zero) {

#pragma unroll

for (int i{0}; i < (N_ARITHMETIC_INSTRUCTIONS / 2); ++i) {

// Each of these instructions sets value to zero

value *= zero;

value &= zero;

value &= zero;

}

return value;

}</pre>

```

Listing 2: Example function that exclusively issues arithmetic instructions. For loop is unrolled to remove branch and jump instructions. The variable zero contains the value zero at runtime, but is set to zero only at runtime to prevent the compiler from optimizing away the instructions in the for loop, as the function would always return zero.

The code of Listing 2 shows a bogus calculation that is repeated multiple times. One of the function parameters is called zero, this variable contains zero at runtime. The zero is not hardcoded, as then the compiler would be able to optimize away the instructions within the for loop. The for loop is also completely unrolled, to avoid any bound checking and branching instructions. The N\_ARITHMETIC\_INSTRUCTIONS constant is divided by two as there are two instructions per iteration. There are two different instructions per iteration, as the compiler can often optimize away a single repeated instruction. The main point of this function is that it exclusively issues a large number of arithmetic instructions.

Listing 3: Example function that exclusively issues memory load instructions. For loop is unrolled to remove branch and jump instructions. The pointer to zero variable points to a variable or array containing a single zero to ensure that the value that is returned is always zero, which will cause repeated accesses to the same memory address. Therefore the memory that is accessed in this function will most probably reside in the L1 cache, as all threads repeatedly access the same value.

The code of Listing 3 also shows a bogus calculation that is repeated multiple times. In this case the additional function parameter ptr\_to\_zero is a pointer to memory that consists of a single zero. As value is set to zero at runtime, it will effectively repeatedly load the same value, so the memory it loads resides in the L1 cache. The function is therefore bound by the memory throughput of the L1 cache. The value is only set to zero at runtime, as otherwise the compiler could optimize away the for loop. The main point of this implementation is that it exclusively issues memory instructions, instead of arithmetic instructions.

Both of these implementations were separately executed by 104,857,600 threads, and the resulting execution times can be seen in Table 3.3. The N\_ARITHMETIC\_INSTRUCTIONS is set to 900, and N\_MEMORY\_INSTRUCTIONS is set to 60. These values were chosen to ensure that the implementations take approximately the same amount of time to execute. Therefore, the execution times in the table are almost the same. This experiment

establishes the execution times of both the functions in isolation.

| Kernel     | Execution time (ms) |

|------------|---------------------|

| Arithmetic | 109.46              |

| Memory     | 106.94              |

Table 3.3: This table shows the execution times of the arithmetic function and memory function in isolation. The number of arithmetic instructions and memory instructions executed by each type of kernel was adjusted to approximately equalize the total execution times of the kernels.

To actually show how we can leverage the fact that warps share a set of heterogeneous instruction pipelines, we construct another kernel, which calls two functions, instead of only one function. There are four variants of this kernel, one where the arithmetic implementation is called twice, one where the memory implementation is called twice, and two variants where the first call uses the arithmetic implementation, and the second call the memory implementation, or vice versa.

| Execution time (ms) |

|---------------------|

| 185.10              |

| 106.06              |

| 112.98              |

| 210.37              |

|                     |

Table 3.4: This table shows the execution times of all variants for a kernel that performs two function calls. Alternating the type of functions is faster than using the same function twice.

In Table 3.4 the results can be seen for all variants of the kernel that performs two function calls. The results table show that, as expected, calling the same function twice will approximately take twice as long as the execution time of that implementation in isolation. However, the execution times for the kernel where the first and second functions execute different types of instructions are faster than twice the execution speed of either implementation in isolation.

This speedup is caused by the fact that the kernel can use the combined throughput of two different instruction type pipelines, instead of only issuing instructions for one instruction pipeline. The fact that warps can be in different stages of the kernel, executing a different type and set of instructions, causes them to not have to wait for access on the same instruction pipeline type. In the kernels where the invocations do not alternate between implementations, both warps will be waiting on the same overloaded arithmetic, or memory instruction pipelines, instead of spreading the load on multiple instruction pipeline types.

#### 3.8 Microbenchmark: Instruction-Level Parallelism

On CPUs, a naive compilation of a program might produce an instruction stream that contains many data or control dependencies between subsequent instructions. Compilers aggressively reorder instructions to exploit as much *instruction-level parallelism* (ILP) as possible. By executing independent instructions in between interdependent instructions, the processor is less likely to need to stall to wait for a dependency on a previous instruction to resolve[21].

GPUs can use occupancy, and switch warps, to hide latency when other warps stall. However this might not always be enough, or result in the most optimal kernels. Increasing ILP can also improve performance of kernels on GPUs. By avoiding stalling altogether, the throughput of individual warps can be increased[57]. The NVIDIA compiler is aware of this concept, and will aggressively reorder instructions to increase the parallelism between long latency instructions as much as possible. Instead of only issuing one read to global memory, and wait for the result, the compiler will put all independent memory instructions next to each other. Instead of needing to stall to wait for each latency, the latencies are overlapped and the warp will receive the results of the other reads roughly by the time the first read is resolved. Although the compiler will reorder instructions to leverage ILP as much as possible, kernels can sometimes be rewritten to expose more ILP for the compiler to exploit.

To show the effect of increasing ILP, and to show that sometimes even 100% occupancy is not enough to hide the latency of instructions, a variant of a pointer chasing benchmark is benchmarked. Pointer chasing benchmarks are often used to measure the latency of memory requests, but are also ideal to show the effect of ILP, because pointer chasing benchmarks almost exclusively consist of interdependent instructions with high latency.

A pointer chasing benchmark repeatedly accesses a large array that consists of a random permutation of the arrays indices. The index of the next array element to fetch is the value of the last array element that was fetched. This ensures that the compiler cannot reorder instructions to overlap latencies, as the address of the next memory access depends on the previous memory access. The latency of a read instruction can then be calculated by dividing the total execution time by the number of pointers chased.

The kernel that will show the importance of ILP on GPUs will let 10,240,000 threads chase 100 pointers each through an array of 10,000,000 elements. This array is too large to fit into the L1 cache or L2 cache of the GPU, and the random walk through the array ensures that most memory reads will need to read their data from RAM. To simplify the benchmark it is ensured that warps will always fetch a single cache line per read instruction by only enabling a single thread per warp. This avoids becoming throughput bound by issuing uncoalesced memory accesses. The warp to array element mapping is given in Figure 3.3. The pointer chasing benchmark will be executed with varying

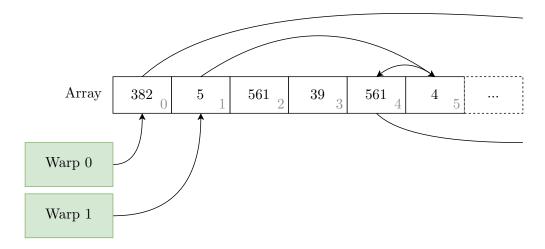

Figure 3.3: Example of how two warps chase pointers through a randomly permuted array of indices. Warp n first fetches the value in the array at index n. Then it retrieves the next value at array[value]. This step is repeated 100 times. To simplify the benchmark measurements, only a single thread is active per warp.

amounts of occupancy. Occupancy is limited by allocating the maximum amount of shared memory per thread block, ensuring that only one or two thread blocks per SM are active. Then the desired occupancy can be configured by increasing or decreasing the number of threads per thread block.

The experiment will be repeated with varying amounts of ILP. ILP is increased in this case by letting a single thread concurrently chase multiple pointers. The number of launched threads is then decreased proportionally, to ensure that the total amount of pointers chased remains the same. Figure 3.4 depicts this new warp to element mapping, and Listing 4 shows the core code for this benchmark. The compiler is able to reorder the instructions to overlap memory read latencies if the ILP\_FACTOR is higher than 1.

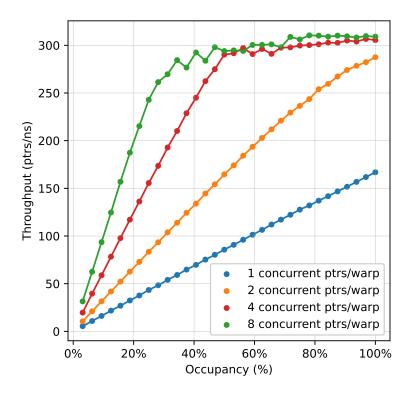

Figure 3.5 shows how effective exposing ILP to the compiler can be. In this kernel that mainly consists of instructions with very high latency, improving ILP is a strict improvement for each ILP factor. By chasing only a single pointer per thread, the maximum throughput is not even reached at 100% occupancy. Maximum throughput can only be obtained by chasing multiple pointers concurrently. For any level of occupancy, increasing ILP gives a higher throughput. With an ILP factor of 8, maximum throughput can already be obtained with an occupancy of just 40%.

In conclusion this microbenchmark shows that ILP is not only relevant on CPUs, but also on GPUs. Exposing more ILP to the compiler can be necessary at even 100% occupancy to reach optimal performance in latency bound kernels. Increasing ILP does not improve kernels that are throughput bound, as overlapping latencies is not needed when instruction pipelines are already saturated. Latency bound kernels can also be rewritten to focus less on reaching 100% occupancy, because with more ILP less occupancy is needed to offset long latency. Being able to focus less on occupancy opens up more design space for other optimizations.

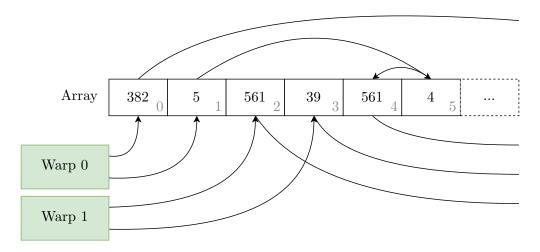

Figure 3.4: Example of how two warps chase multiple pointers through a randomly permuted array. In this case each warp chases two pointers through the array. Warp n now starts at index n\*m when each warp chases m pointers. When chasing multiple pointers, each warp can concurrently issue the read instructions for each pointer, without waiting for the previous read to finish. The total amount of activated warps is proportionally decreased, to correct for the fact that each warp chases multiple pointers. The total amount of pointers chased remains constant.

```

template <unsigned CHASE_N_PTRS, unsigned ILP_FACTOR>

__device__ int chase_ptr(const int *array, int* chasers) {

#pragma unroll

for (int i{0}; i < CHASE_N_PTRS; ++i) {

#pragma unroll

for (int v{0}; v < ILP_FACTOR; ++v) {

chasers[v] = array[chasers[v]];

}

}

}</pre>

```

Listing 4: Function that chases multiple pointers concurrently through an array. For loops are unrolled to avoid branch and jump instructions, as well as to allow the compiler to put all the memory load instructions next to each other in the generated assembly. The ILP\_FACTOR variable indicates how many pointers are concurrently chased.

Figure 3.5: Increasing the ILP factor in benchmark increases throughput at any level of occupancy. Maximum memory read throughput can be reached with occupancy levels lower than 100%. Maximum memory read throughput is not reached, even at 100% occupancy, when each warp only chases 1 pointer concurrently.

## Chapter 4

# GPU Decoding Algorithms

This chapter explains how the FastLanes and ALP algorithms, that were designed to leverage SIMD instructions on CPUs, are redesigned to perform well on GPUs. The chapter starts off with studying what the initial implementation of FastLanes on GPUs did, and then explains both the advantages as well as the disadvantages of that implementation. To solve the disadvantages, a new implementation is proposed that decodes values one at a time, instead of entire vectors.

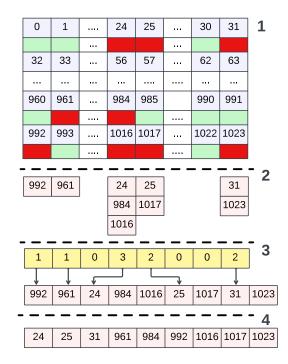

This chapter studies how ALP's CPU exception patching approach can be optimized by decoding one value at a time. After that a section follows which explains how the exception layout can be improved to allow for more data-parallelism during the patching of exceptions. The chapter concludes with an explanation of a minor performance improvement on the decoding algorithm of the data-parallel exception layout.

## 4.1 FastLanes Decoding

Regular FastLanes decodes entire vectors at a time, and all of the necessary decoding steps are based on the bitwidth that was used to pack, encode, the vector with. The implementation uses switch statements to the correct hardcoded block of instructions for a specific bitwidth. There is a hardcoded block for each possible bitwidth including 0. Algorithm 1 shows the pseudocode for this decoding approach. The initial FastLanes GPU implementation is copies the CPU implementation, except that each thread only decodes a single lane within a vector.

The hardcoded instruction blocks contain no redundant instructions, and the order of instructions can be fully optimized by the compiler. As most of the hardcoded instructions are independent of each other, the compiler can exploit instruction-level parallelism by grouping independent instructions together. Especially important is that all the load instructions can be grouped together, ensuring that the load latencies are overlapped and thus much cheaper. The hardcoded instruction blocks can be reached efficiently, as there is only a single branch, and the branching cost can be amortized

#### Algorithm 1 FastLanes lane decoding

```

1: PACKED\_VECTOR\_POINTER \leftarrow load(PACKED\_VECTOR\_POINTER + LANE)

2: DECODED_INTEGERS [32]

3: switch BIT_WIDTH do

case 1

4:

PACKED_INTEGER ← load(PACKED_VECTOR_PTR + 0)

5:

6:

▶ Hardcoded instructions to unpack into DECODED_INTEGERS

7:

break

case 2

8:

FIRST_PACKED_INTEGER ← load(PACKED_VECTOR_PTR + 0)

9:

10:

SECOND_PACKED_INTEGER ← load(PACKED_VECTOR_PTR + 32)

11:

▶ Hardcoded instructions to unpack into DECODED_INTEGERS

break

12:

case 3

13:

14:

FIRST_PACKED_INTEGER \leftarrow load(PACKED_VECTOR_PTR + 0)

SECOND_PACKED_INTEGER ← load(PACKED_VECTOR_PTR + 32)

15:

THIRD_PACKED_INTEGER ← load(PACKED_VECTOR_PTR + 64)

16:

▶ Hardcoded instructions to unpack into DECODED_INTEGERS

17:

break

18:

▷ Continue for all other bitwidths

19:

20: return DECODED_INTEGERS

```

across all values in that vector.

However, decompressing one lane per thread is undesirable on GPUs as it requires an output array of 32 or 64 values. This heavily increases register pressure, reducing occupancy. In specialized kernels this might not be problematic, but as the goal is to produce a decoding API for general use, the API should not put limitations on occupancy.

Hence, the goal is to design an API that can decompress vectors one value at a time. This would require no output array, but a single register to store the result in, thus decreasing the register pressure of the API.

#### 4.1.1 Single Value Decoding

The single value decoding API decodes the values in a lane in order. Every time the decoding function is called, the next value in the lane is decoded. When decoding a single value at a time, the switch statement based approach becomes more complex. Instead of a single branch on the bitwidth, an additional branch is now needed to pick the right instructions to decode that specific position in the lane. The cost of a single branch is no longer amortized over 32 values, but instead it is needed to branch twice every time a value is decompressed.

Splitting up the code blocks into code blocks that decode a single value also removes the benefits of hardcoded instructions. No longer can the loads be trivially grouped next to each other due to the control hazard of the new branches. This removes the huge advantage of putting all loads together. You still retain the benefit of executing only the bare necessary instructions within those code blocks, but database kernels that benefit from compression on the GPU are limited by memory read throughput during decoding, not by compute throughput.

The number of hardcoded instruction blocks also increases. 32-bit types requires 32-bitwidths multiplied by 32 positions, is 1024 blocks. 64-bit types requires 64-bitwidths multiplied by 64 positions, is 4096 cases. This would heavily increase the binary size, especially considering that the compiler aggressively inlines functions as function calling is expensive on GPUs. Additionally, instruction cache latency might become a problem, because for each uniquely used bitwidth in the data, the common set of instructions grows, potentially larger than the instruction cache.

Instead, the GPU implementation of FastLanes single value decoding uses a more simple approach using branches, as shown in Algorithm 2. The implementation continuously buffers an integer from the packed vector, that contains multiple encoded values. Each time the decoding function is called, the next packed value is extracted from the buffer. When all values from a buffer are loaded, the buffer is refreshed by loading the next packed integer from the packed vector. If an encoded value spans multiple packed integers, the remaining bits from the next buffer are fetched and combined with the bits from the initial buffer.

The buffer can reside in cache, local memory, registers, or shared memory. The buffer can also be expanded to multiple packed integers. In that case refreshing the buffer executes two or more reads at a time, enabling the compiler to overlap the latencies of the two reads. When the first buffer is fully decoded the decoder will decode the second buffer before refreshing both buffers simultaneously.

#### Algorithm 2 FastLanes single value decoding

Phase - Initialization

1: BUFFER ← load\_next\_packed\_integer()

Phase - Decode one value

```

2: DECODED_INTEGER ← UNPACK_INTEGER_FROM(BUFFER)

3: if BUFFER_IS_EXHAUSTED then

4: BUFFER ← load_next_packed_integer()

5: if PACKED_INTEGER_SPANS_TWO_LINES then

6: UNPACKED_REMAINING_BITS ← (UNPACK_INTEGER_FROM(BUFFER) << OFFSET)

7: DECODED_INTEGER ← DECODED_INTEGER | UNPACKED_REMAINING_BITS

8: end if

9: end if

10: return DECODED_INTEGER

```

The downside of the approach in Algorithm 2 in comparison to Algorithm 1 is that there are more instructions needed, as the implementation cannot rely on specialized hardcoded blocks of instructions. Additionally, this implementation contains branches.

However, compute throughput is not the bottleneck on GPUs when decoding for most value bit widths.

#### 4.1.2 Branchless Single Value Decoding

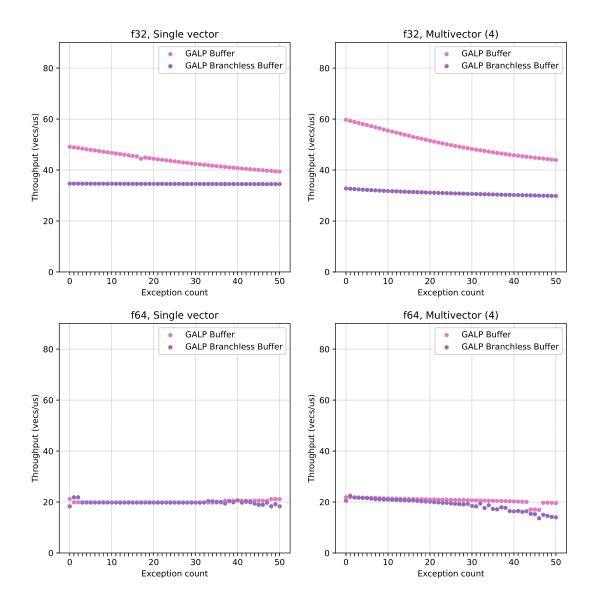

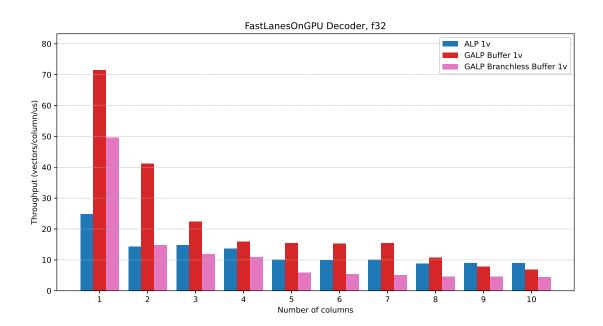

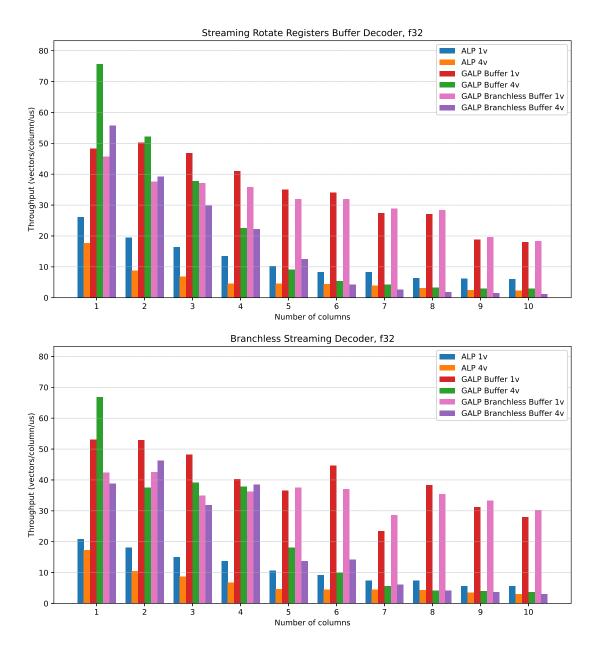

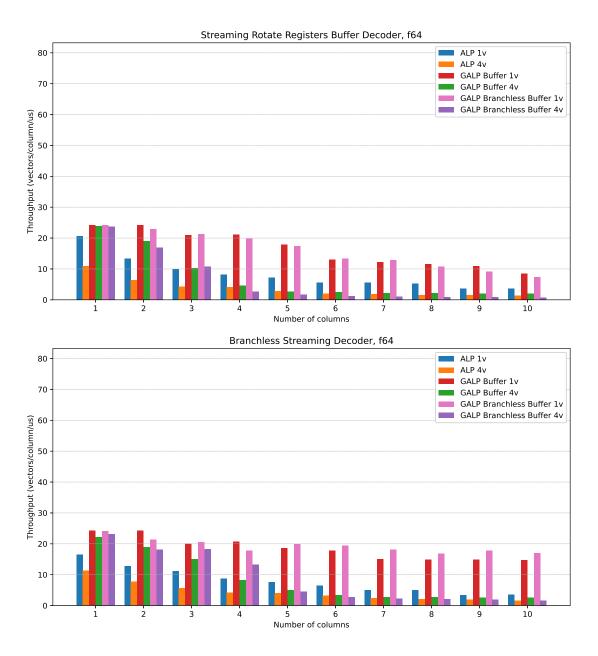

11: return DECODED\_INTEGER