# Universiteit Leiden Opleiding Informatica

Virtual Machine

### for Secure Embedded Systems

Name:

Manuel Spierenburg

Date: 05/08/2017

1st supervisor:Dr. ir. Todor Stefanov2nd supervisor:Dr. Teddy Zhai2nd reader:Dr. Kristian Rietveld

MASTER'S THESIS

Leiden Institute of Advanced Computer Science (LIACS) Leiden University Niels Bohrweg 1 2333 CA Leiden The Netherlands

## Acknowledgments

First of all I want to thank Teddy Zhai who helped and supported my throughout the work of this thesis. Even after he already left the company, where I was working on this project, he guided me and helped me to finish. Without him this would not have been possible.

Also I want to thank Vladimir Zivkovic for giving me this project which gave me the opportunity to finish my master program. Further I want to thank Irdeto B.V. for giving me the time and equipment, especially the access to the ST platform, which allowed me to conduct the experiments for this thesis.

Last but not least I want to thank Todor Stefanov and Kristian Rietveld for giving my advice and for their patience.

#### Abstract

In the Broadcasting and Over-The-Top media-service industries, video content which is delivered to the customer needs to be secured by encrypting or scrambling the content. The content then needs to be decrypted or unscrambled at the end-users location. A common technique is to use a hardware device which includes a secret key for the cryptographic operations. Many television providers use a Set-top Box (STB) which is installed at the end-users home to execute this task. The security of the decryption or descrambling method is enforced in the Set-top box by a Secure Chipset which resides on a System on a Chip (SoC) in the Set-top box. In the market of Digital Video Broadcasting (DVB) or HTTP Live Streaming (HLS) many different chip vendors compete. The vendors develop their own framework and Application Programming Interface (API) which have to be used by the Conditional Access System (CAS) and Digital Rights Management (DRM) vendors. The hardware design and implementation decisions are left with the Silicon Vendor. This leads to fragmentation and the CAS and DRM vendors need to integrate with many different solutions. Often broadcasting companies have many different Set-top Boxes with different Chips deployed in the field. Updates for the program which runs on the Secure Chipset therefore have to be developed and tested for the different chip types. This leads to raising costs as, for each chip type, a different image has to be produced. Further in the world of Satellite communication it is not possible to unicast an image to a specific STB. All images are broadcast to all the STBs and the STB itself decides which image to use. It is not uncommon that six to ten different images have to be broadcast to all the STBs which leads to a significant increase of bandwidth. In the case of satellite communication this bandwidth usage is very expensive and undesired. In this thesis we propose a solution to decrease this bandwidth by creating an abstraction layer between the Secure Chip and the image running on the chip. We created a Virtual Machine (VM) which can interpret a suitable instruction set. This VM has to be integrated with the different chip vendors only once during production of the chip. The image which runs then on the VM can be deployed in later stages. The benefit is that only one image has to be produced and broadcast to the STBs which leads to decrease of the used bandwidth. In this thesis we analyze the code size and performance penalty of the VM compared to a native application running on a secure chip.

## Contents

#### Abbreviations

| 1        | Intr | roduction 5                                      |  |  |  |  |  |  |  |  |

|----------|------|--------------------------------------------------|--|--|--|--|--|--|--|--|

|          | 1.1  | 1 Broadcasting Service                           |  |  |  |  |  |  |  |  |

|          | 1.2  | Television Encryption                            |  |  |  |  |  |  |  |  |

|          | 1.3  | Conditional Access Systems                       |  |  |  |  |  |  |  |  |

|          |      | 1.3.1 Scrambling                                 |  |  |  |  |  |  |  |  |

|          |      | 1.3.2 Transmitting Control World                 |  |  |  |  |  |  |  |  |

|          |      | 1.3.3 Transmitting Access Information            |  |  |  |  |  |  |  |  |

|          |      | 1.3.4 Protection of ECM and EMM                  |  |  |  |  |  |  |  |  |

|          |      | 1.3.5 Set-top Box Architecture                   |  |  |  |  |  |  |  |  |

|          | 1.4  | Secure Chip Design                               |  |  |  |  |  |  |  |  |

|          | 1.5  | Problem Description                              |  |  |  |  |  |  |  |  |

|          | 1.6  | Solution Approach                                |  |  |  |  |  |  |  |  |

|          | 1.7  | Thesis Contribution                              |  |  |  |  |  |  |  |  |

|          | 1.8  | Related Work                                     |  |  |  |  |  |  |  |  |

|          |      | 1.8.1 Self Protecting Digital Content            |  |  |  |  |  |  |  |  |

|          |      | 1.8.2 Terra Trusted Virtual Machine 14           |  |  |  |  |  |  |  |  |

|          |      | 1.8.3 Virtual Machine for Microcontrollers       |  |  |  |  |  |  |  |  |

|          |      | 1.8.4 Tiny Virtual Machine for Sensor Networks   |  |  |  |  |  |  |  |  |

|          |      | 1.8.5 ARM TrustZone                              |  |  |  |  |  |  |  |  |

| <b>2</b> | Bac  | ckground 18                                      |  |  |  |  |  |  |  |  |

|          | 2.1  | Virtual Machines                                 |  |  |  |  |  |  |  |  |

|          |      | 2.1.1 Process And System VMs                     |  |  |  |  |  |  |  |  |

|          | 2.2  | Instruction Sets                                 |  |  |  |  |  |  |  |  |

|          |      | 2.2.1 MIPS Instruction Set                       |  |  |  |  |  |  |  |  |

|          |      | 2.2.2 ARM Instruction Set                        |  |  |  |  |  |  |  |  |

|          | 2.3  | Comparison between MIPS and ARM Instruction Sets |  |  |  |  |  |  |  |  |

|          | 2.4  | Security of Embedded Systems                     |  |  |  |  |  |  |  |  |

| 3        | Des  | sign and Implementation 35                       |  |  |  |  |  |  |  |  |

| 0        | 3.1  | VM Software Design                               |  |  |  |  |  |  |  |  |

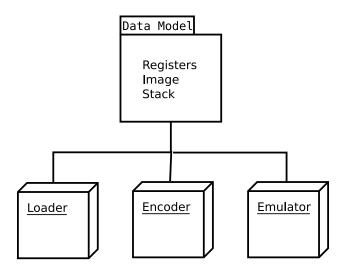

|          | 0.1  | 3.1.1 VM Data Model                              |  |  |  |  |  |  |  |  |

|          |      | 3.1.2 VM Image Loader                            |  |  |  |  |  |  |  |  |

|          |      | 3.1.3 VM Encoder                                 |  |  |  |  |  |  |  |  |

|          |      | 3.1.4 VM Emulator                                |  |  |  |  |  |  |  |  |

|          |      | 3.1.5 System Calls                               |  |  |  |  |  |  |  |  |

|          | 3.2  | Additional Instruction Sets       39             |  |  |  |  |  |  |  |  |

|          | 3.3  | Virtual Machine Runtime                          |  |  |  |  |  |  |  |  |

3

|    |                                  | $3.3.1 \\ 3.3.2$                  | MIPS Virtual Machine Runtime | $40 \\ 42$                                    |  |  |  |  |  |

|----|----------------------------------|-----------------------------------|------------------------------|-----------------------------------------------|--|--|--|--|--|

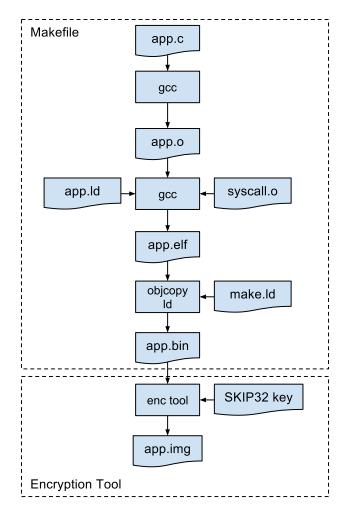

|    | 3.4                              | 0.0                               | cation Image                 | $42 \\ 43$                                    |  |  |  |  |  |

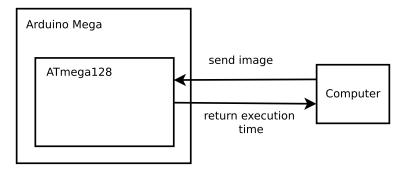

| 4  |                                  |                                   | lies And Experimental Setup  | 44                                            |  |  |  |  |  |

|    | 4.1                              | Exper:<br>4.1.1<br>4.1.2          | imental Applications         | $\begin{array}{c} 44 \\ 44 \\ 45 \end{array}$ |  |  |  |  |  |

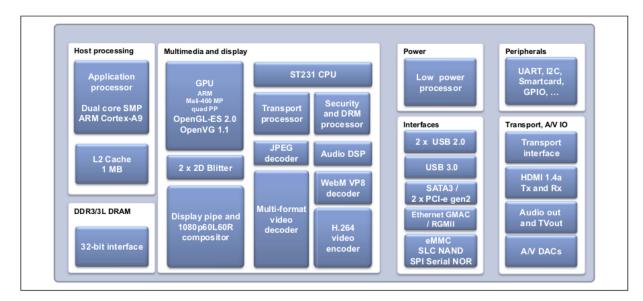

|    | 4.2                              | Exper<br>4.2.1                    | imental Platforms            | 46<br>46                                      |  |  |  |  |  |

|    | 4.3                              | 4.2.2<br>Create<br>4.3.1<br>4.3.2 | ST Platform                  | 48<br>49<br>50<br>51                          |  |  |  |  |  |

| 5  | Exp                              |                                   | nts and Results              | 53                                            |  |  |  |  |  |

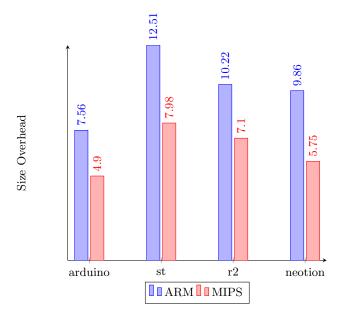

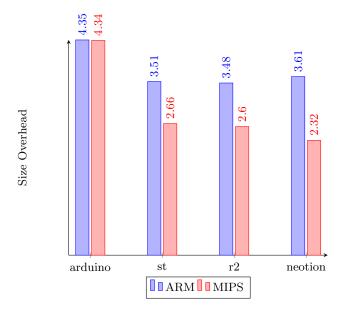

|    | 5.1<br>5.2                       | $5.1.1 \\ 5.1.2$                  | Size Overhead of VM          | 53<br>53<br>55<br>57<br>57                    |  |  |  |  |  |

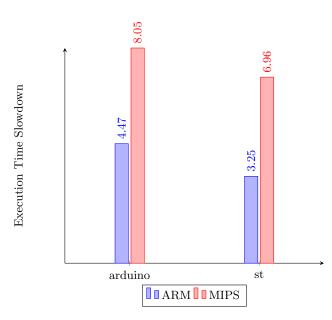

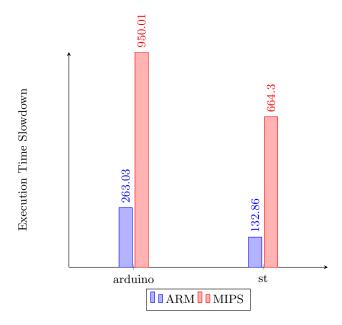

|    | 5.3                              | 5.2.2<br>Execu                    | Application 2                | $\frac{58}{60}$                               |  |  |  |  |  |

| 6  | Con                              | clusio                            | n                            | 61                                            |  |  |  |  |  |

| 7  | Fut                              | ure W                             | ork                          | 62                                            |  |  |  |  |  |

| Bi | Bibliography 65                  |                                   |                              |                                               |  |  |  |  |  |

| Α  | A MIPS 1 Instructions            |                                   |                              |                                               |  |  |  |  |  |

| В  | MI                               | PS 1 E                            | ncoding                      | 68                                            |  |  |  |  |  |

| С  | C ARMv6 Cortex-M0 Instructions 7 |                                   |                              |                                               |  |  |  |  |  |

| D  | D ARM Encoding 7                 |                                   |                              |                                               |  |  |  |  |  |

## Abbreviations

**ABI** Application Binary Interface. ACPU Application Central Processing Unit. ALU Arithmetic Logic Unit. **AM** amplitude modulation. **API** Application Programming Interface. **APRS** Applicatoin Program Status Register. **ARM** Advanced RISC Machine. CAS Conditional Access System. **CISC** Complex Instruction Set Computing. **CPU** Central Processing Unit. **DBS** Direct-broadcast Satellite. **DRM** Digital Rights Management. **DVB** Digital Video Broadcasting. **DVB-CI** DVB Common Interface. **ECM** Entitled Control Word Message. EMM Entitled Management Messages. **FM** frequency modulation. HLS HTTP Live Streaming. **ISA** Instruction Set Architecture. **OTA** Over The Air Broadcasting. PC Program Counter.

${\bf RISC}\,$  Reduced Instruction Set Computing.

SCPU Secure Central Processing Unit.

SoC System on a Chip.

STB Set-top Box.

TA Trusted Application.

TEE Trusted Execution Environment.

TVMM Trusted Virtual Machine Monitor.

VLIW Very Long Instruction Word.

VM Virtual Machine.

VMM Virtual Machine Monitor.

### Chapter 1

## Introduction

In this chapter we provide background information about broadcasting of video content and how it is secured. Further in Section 1.5 we discuss the problem and the research questions. In the following section the solution approach is described. In addition we present some related work in the field and compare it to our approach in Section 1.8.

#### 1.1 Broadcasting Service

Broadcasting describes the distribution of media content such as audio or video to customers in a one to many model. For the distribution of the content, different communication systems were used over the years. The first broadcast system used radio transmitter and receivers to transmit content via radio signals over the air. This kind of broadcasting is also called Over The Air Broadcasting (OTA) or terrestrial transmission. The signal transmitted thereby was an analog signal. In analog broadcasting, all channels are broadcast at the same time. The receiver then has to filter the signal to enable the end user to consume the desired channel. The separation of the different channels is achieved by modulation, either frequency modulation (FM) or amplitude modulation (AM). For example with frequency modulation, the signal of a channel is encoded into the radio signal with a dedicated frequency. The receiver then can receive the specific channel by separating out the signal on the dedicated frequency. Later on cable transmission was introduced which allowed to broadcast more channels with less interference. Often the cable providers use local satellite stations and distribute the signal from there over cables to the customers. Another possibility is when the customer has a satellite receiver and directly connects to the broadcast satellite. This kind of transmission is also called Direct-broadcast Satellite (DBS). This new broadcasting techniques allowed to enable new business models where the customers pay for subscription. This in return introduced new requirements on the security of the broadcast signal. To prevent users without subscription stealing the signal, new security measures had to be implemented.

#### **1.2** Television Encryption

The access to television services is secured by encrypting the signal. In television this method is often also called "scrambling". In the beginning television encryption involved filtering out channels to users without subscription. With more channels available and more users with subscription, this system became unmanageable. Newer systems introduced interference signals to channels and users with subscription needed a set-top box to descramble the signal. But these analog encryption systems were all broken. With the rise of digital television more sophisticated encryption mechanisms were introduced.

#### **1.3** Conditional Access Systems

Conditional Access System (CAS) describe a whole system which is used in digital television to protect content. The system can control subscriber access to services, programmes and events. Generally a CAS system consist of two subsystems. A scrambling subsystem which scrambles and descrambles the media content for only subscribed users, and an access control system which determines if descrambling of the content is allowed. An international standard for conditional access systems (DVB-CA) has been introduced which includes a Common Scrambling Algorithm (DVB-CSA) and a Common Interface (DVB-CI) for access control. The content in the standard is secured with a control word key of 128 bits. The encryption algorithm itself is based on a two block cipher where the first algorithm is a variation of the AES128 cipher called AES' and the second algorithm is a confidential cipher called eXtended emulation Resistant Cipher (XRC). The control word itself is derived from another key and changes several times per minute.

#### 1.3.1 Scrambling

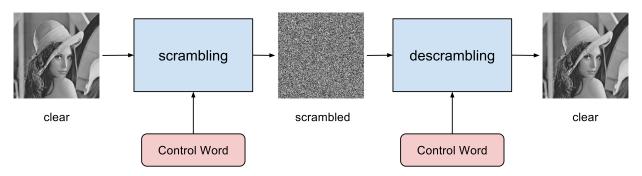

Figure 1.1: Scrambling with Control Word

In a Digital Video Broadcasting (DVB) system the clear signal is encrypted with a key in a scrambler. Usually this happens in a multiplexer or IP Streamer at the head end of the system. The key is defined in the CAS algorithm as Control Word. The descrambler at the user end has to use the same control word to be able to decrypt the signal again as shown in Figure 1.1. Usually this is done in the Set-top Box (STB).

The Control Word is chosen by the scrambler. For security reason the Control Word changes several times per minute between two different Control Words. In the header of the transport stream two bits are reserved to identify which Control Word is used or if the stream is not encrypted.

| Bit values | Description                                                         |

|------------|---------------------------------------------------------------------|

| 00         | No scrambling of transport stream packet payload (MPEG-2 compliant) |

| 01         | Reserved for future DVB use                                         |

| 10         | Transport stream packet scrambled with Even Key                     |

| 11         | Transport stream packet scrambled with Odd Key                      |

Table 1.1: Control Word in Transport Stream

#### 1.3.2 Transmitting Control World

The Control Word is generated in the scrambler and needs to be sent to the descrambler. This is achieved with the help of an Entitled Control Word Message (ECM). The ECM again is encrypted in a proprietary way known to the CAS system vendor and sent over the transport stream.

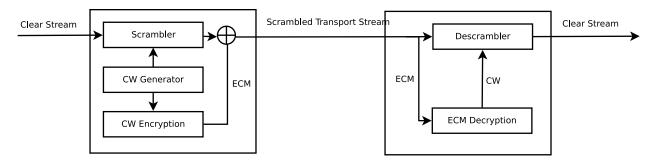

Figure 1.2: Transmitting the Control Word

The components which are used to transmit the control word are depicted in Figure 1.2. In the scrambler module two control words (CW) are generated which are used to scramble the clear media stream. These control words are then encrypted and send together with the scrambled transport stream to the end user. Typically the ECM contains two control words, time information and channel identification. The time and channel information can be used inside the STB to identify if the User is allowed to access a certain channel during this time. Each Channel has its own ECM. Therefore before the STB can decrypt the signal it needs to receive the ECM for the channel. This leads to a short latency after the channel is switched on the STB and until the channel can be descrambled and shown to the customer. To reduce this latency when the channel is changed the ECMs are repeated every 100ms.

#### 1.3.3 Transmitting Access Information

The access information of the the CA system is needed to determine if the user has the rights to access a certain channel or not. The DVB system needs to send access information to the STB for example when a user signs up for a new channel. The messages sent include information such as, allow this user to watch this channel for the next month or allow this user to watch this movie. This information is sent to the STB with the help of Entitled Management Messages (EMM). The EMMs are then used by the STB to update their internal access control database.

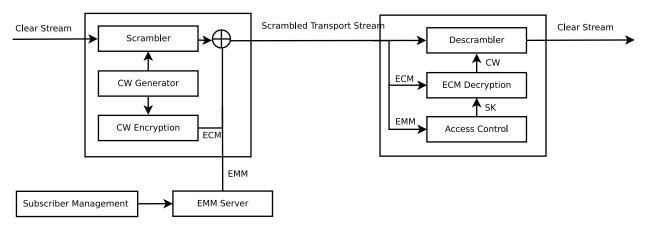

Figure 1.3: Transmitting the Access Information

Figure 1.3 shows all components which are used to transmit an EMM. When the subscriber information is changed in the management system, new EMMs are generated. The EMMs are then inserted into the transport stream with the help of a multiplexer. In the STB the EMMs are consumed by the access control system. Together with the information in the ECM (date and channel information) the access control system decides if the user is allowed to descramble this content. The content of the EMM is proprietary and differs by CAS vendor.

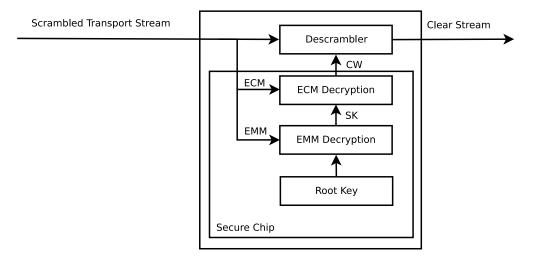

#### **1.3.4** Protection of ECM and EMM

The protection of ECM and EMM messages is not defined in the DVB standard and is defined by the CAS vendor. A common technique is that the EMM messages are encrypted with a root key. This scenario is shown in Figure 1.4. In the STB, the EMM is decrypted with help of the root key. The EMM then contains a session key (SK) which is used to decrypt the ECM messages. The decrypted ECM message at the end contains the Control Word (CW) which is needed to descramble the media content. The root key is a key which resides in the STB. This can be a key which is implemented on a secure chip. This chip can either be directly in the STB or inside a smart card which can be connected to the STB.

Figure 1.4: Protection of ECM and EMM messages

#### 1.3.5 Set-top Box Architecture

Set-top Boxes are deployed in the field by television companies to perform the descrambling of the encrypted television signal. Modern Set-top Boxes are very powerful and real multitask machines. Decryption of the TV signal thereby is only one part. A STB has to manager user data, record a program so it can be viewed later on, access services for video on demand, download and display additional data from the internet and so on. To be able to process this tasks at the hearth of the STB is a powerful Application Central Processing Unit (ACPU). Usual tasks of this ACPU are:

- Initialize hardware components of the STB

- Fetch updates from the internet

- Monitor and process hardware interrupts

- Store user data and configurations in a database

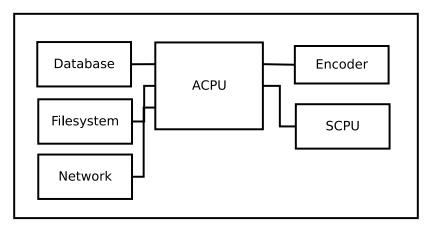

This allows software developers to quickly respond to market changes and create new tools for the STB. Although the ACPU is very powerful in general, many tasks are offloaded to special hardware modules. For example the decryption and decoding of the video signal is very time critical and this functionality is commonly offloaded to a special MPEG decoder unit. Another problem that occurs is the security of the ACPU. The security of the chip relies on the software security. Further as this chips have to perform so many tasks, they have mostly access to various components such as a database, file system and a network card. These factors increase the vulnerability and make these units not suitable for secure implementation of the conditional access system. Therefore, a Secure Central Processing Unit (SCPU) is introduced which can be accessed from the ACPU with a defined protocol. The separation of the components is depicted in Figure 1.5. The ACPU is considered to be non secure and has access to all resources. The encoder and the SCPU are segregated from other resources for security reason.

Figure 1.5: Set-top Box Components

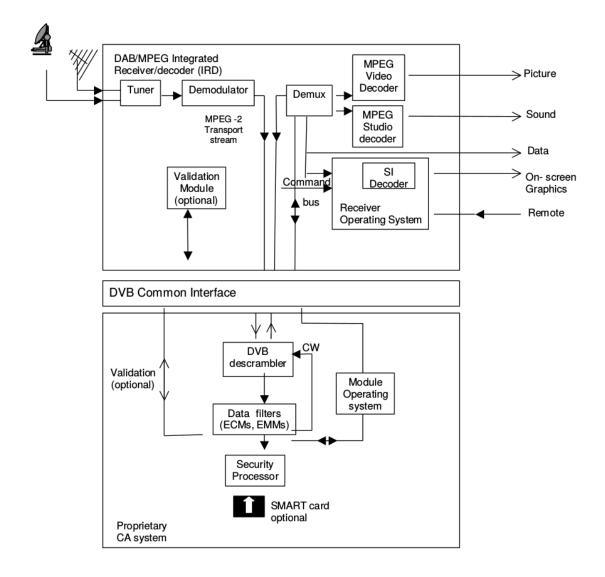

In terms of software we can define two main components in a STB, the operating system and the conditional access system. The operating system includes the main system including a kernel which is startup when the STB is powered on. This OS manages different resources, interacts with hardware components like tv tuner, displays a graphical user interface and processes commands sent via the remote control. At the moment no standard STB OS exists. Broadcasters and STB manufacturers build their own operating system which are often based on either Linux or Windows. These systems are generally hard to secure and are not suitable for the conditional access system. The CA system itself resides on the secure chip which provides protection against attacks and tampering. The DVB Common Interface (DVB-CI) defines the connection between the operating system and the CA system. This standard enables the interoperability of STB models between different CAS vendors. A television company can choose between different STB models and combine it with the CAS system of choice if they follow the standard.

Figure 1.6: Set-top Box Architecture [17]

Figure 1.6 shows the different components of a STB and their separation in more details. Tuner, Demultiplexer, Inputs and Outputs are operating in the general non-secure part. The common interface defines the connection between the general part and the conditional access system. The conditional access system consists of modules to decrypt additional data such as ECMs and EMMs and the DVB descrambler. The implementation of these modules rely on the secure chip implementation of the STB vendor. The CAS vendor therefore has to integrate with multiple STB vendors which are used by the cable company. When a CAS system is compromised it needs to be updated to restore the confidentiality and security of the system. Updates to the CAS system are sent over the transport stream which also is used to send video content and ECM and EMM data. Therefore this stream is already very utilized and any additional data reduces the throughput of other data. If a CAS system is broken it needs to be updated for all models which support this CAS system. This leads to several downsides. For each model a different update needs to be generated for the specific architecture of the secure chip technology. Further because of the architecture of the transport stream, the specific update can not be unicast to the STB which needs the update, but all updates for all models have to be send to all STBs. The STB then needs to pick which update can be installed. It is not uncommon that a CAS vendor needs to integrate with 6 to 10 different STB models for a customer. This means that 6 to 10 different updates are broadcast over the transport stream to the STBs.

#### 1.4 Secure Chip Design

Secure Chips provide another level of physical protection to keep keys and encoded content secure. In a normal processing unit the secret key which is used to decode a content needs to be loaded into the RAM at a certain moment so it can be used. For this purpose the key is transferred in unencrypted over a bus to the RAM. An intruder can monitor the bus and get access to the secret key. This problem can be solved with a Secure Chip. The secure chip has an internal RAM and ROM. In the ROM the initial program and a root key resides. This information is burned into the chip during manufacturing and can not be changed afterwards. To prevent that a malicious application running on the Secure Chip accesses the root key, a secure bootloader which starts the program ensures that only the genuine program has access to the root key. When the initial program is loaded further secret keys which are protected with the root key can be decrypted and loaded into the secure RAM. The bus during this operation can not be monitored.

And ideal Secure Chip has the following properties:

- The ROM and RAM cannot be physically accessed

- The buses inside the chip can not be monitored

- Tampering or removing components invalidates the chip

#### 1.5 **Problem Description**

One of the challenges which occurs nowadays is how to update the software (images) which run on the Secure Chip. This can be necessary when new encryption techniques for the video streams are required. In the market of DVB devices many different silicon vendors compete. Each vendor provides their own solution and compete in performance, security and utilisation of silicon with the other competitors. The above mentioned battle leads to a fragmentation of different secure-silicon devices where CAS and Digital Rights Management (DRM) vendors have to integrate with. Often broadcasting companies have many different Set-top Boxes with different Chips deployed in the field. Updates for the program which runs on the Secure Chipset therefore have to be developed and tested for the different chip types. This leads to raising costs as for each chip type a different image has to be produced. Further in the world of Satellite communication it is not possible to unicast an image to a specific STB. All images are broadcast to all the STBs and the STB itself decides which image to use. This leads to a significant increase of bandwidth. In the case of satellite communication this bandwidth usage is very expensive and undesired. The increasing diversity of secure chips and the resulting increase in needed bandwidth to update devices for broadcasting services is the problem we want to investigate in this thesis.

#### 1.6 Solution Approach

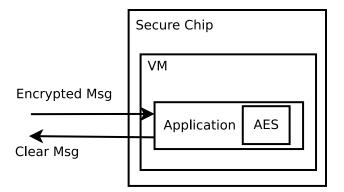

To try solving the problem of many different secure chip software implementations, we propose to add an abstraction layer on top of the secure chip. As abstraction layer we propose a Virtual Machine (VM) which can interpret a suitable instruction set. We define the architecture on which the VM is running as the *host architecture* and the architecture which is interpreted by the VM as the *guest architecture*. Further we call applications which run on top of the VM *images*. Images are programmed for the guest architecture which can be interpreted by the VM. By using an established instruction set architecture as guest architecture we give more flexibility to developers for changes in the future. A developer can implement code in the language of choice and compile it to the guest instruction set which can be understood by the VM.

Further, by using already established instruction sets, common tools can be used to execute these tasks. As the virtual machine needs to be ported to several different host architectures, we decided to create an emulation VM written in C. This allows fast porting of the VM by just compiling it to the desired host architecture. This will cause performance decrease, but the advantage of this solution is the portability of the VM to other secure chip architectures. Another advantage of the emulation approach is that it allows to add further security measures. For example we added another encryption of the instructions of the image which is running on the secure chip. With this approach the image can be loaded over an insecure channel to the secure chip and only the VM on the secure chip can decrypt and interpret the instructions of the image.

To evaluate the above described solution approach we want to answer the following research questions.

- Is it feasible to create an abstraction layer for Secure Chips to run applications on?

- What guest instruction set is suitable for the abstraction layer?

- How large is the code size overhead of the abstraction layer?

- How large is the execution time overhead of the abstraction layer?

For comparison we choose two guest instruction sets which can be intepreted by the VM. We decided to use two established Reduced Instruction Set Computing (RISC) architectures which allow us to use available tools to create the images for the VM.

- MIPS (Microprocessor without Interlocked Pipeline Stages)

- ARM (Advanced RISC Machine)

#### 1.7 Thesis Contribution

In this thesis we developed and run a virtual machine on top of a secure chip. We proved that it is possible to run a virtual machine, as an abstraction layer, on a secure chip. To evaluate the execution time slowdown we used the two platforms, Arduino and ST. Additionally we compared two different instruction sets, ARM and MIPS, from which the ARM instruction set proved to be more suitable. During the analysis of the code size overhead, we discovered that the image size of ARM images are substantially smaller than native images, which would lead to a drastic decrease of bandwidth usage. For example if a broadcaster uses the ARM VM instead of four native applications, up to 80% of bandwidth usage for an application update can be saved.

#### 1.8 Related Work

In this section, we present related work in the field of media protection and virtual machines.

#### 1.8.1 Self Protecting Digital Content

Self-Protecting Digital Content [8] was an architecture developed to secure digital content on optical discs and led to Blue-Ray Digital Right Management system BD+. In the time when optical drives were most popular for content distribution, protecting and securing the content faced several problems. One of the problems was the long live time of the devices and mediums and that the security measures which were for example implemented for DVD were in the hardware and not updatable. When the security was compromised it was not possible to just easy install a new security measure. Another problem was that the device manufacturers were not merely interested in creating the most secure devices as if the content was compromised it did not lead to less revenue for the device manufacturer but alone for the content provider. Moreover, less secure devices which were able to play DVD disregarding of the country code were more attractive for customers to buy than more restrictive one. The content provider should have taken control to develop a secure architecture. The above mentioned not ideal condition led to the not very successful DRM system for DVDs called Content Scramble System (CSS). The system was introduced in 1996 and was first compromised in 1999. CSS was implemented in the player with a fixed security policy for all content. With a valid key all media could be decrypted. To achieve this, the keys were preloaded in the device. One of the design flaws in CSS was that a proprietary cryptographic algorithm was used which proved to be trivial to break. But even though if a strong unbreakable known cryptographic algorithm would have been used often poorly implemented key management allowed attackers to extract the keys without the need of breaking the cryptographic algorithm.

After the failure of CSS, a study proposed the solution of Self-Protecting Digital Content [8]. The idea is to include the security in the content itself and not implement it in the device. This would allow content providers to react to new threats. If a security system is compromised it would be only compromised for the specific content. New content could include updated security measures without updating the player.

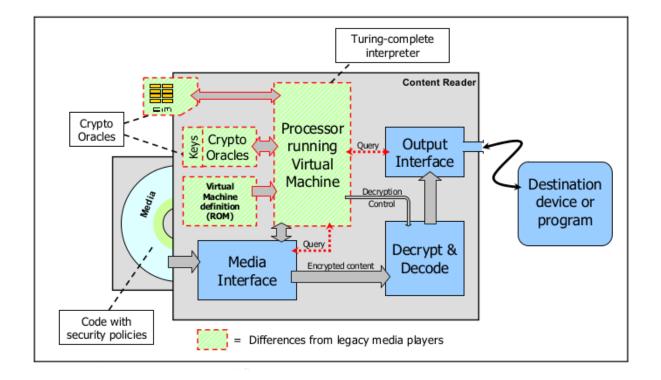

Figure 1.7: DVD protection [8]

The proposed implementation consist of a virtual machine, as seen in Figure 1.7, which has access to cryptographic modules with keys. Further the virtual machine has an interface to the control unit and can control how the content is decrypted and played to the output of the system. The code which determines how the video content is decrypted is also on the disc and loaded in advance in a secure way to the ROM of the VM. This decrypting code resides on the VM and loads the content, decrypts it and sends it to the output of the device.

Even though this technology was developed for content on optical discs which are a little bit outdated nowadays, similar techniques can be adopted to the over the top content distribution. A VM on a device or in a software player can preload descramble information which is included in the content which is send to the customer. The preloaded code includes the security measures which allow the user to see the content. This technology also provided a virtual machine with many special system calls which allowed the developers of the DRM software to access other components of the STB. The developed virtual machine was designed for a special chip and was not designed for portability. The main goal was not to emulate a different instruction set but to offer a platform to content providers to secure their content.

The goal of our VM on the other hand is to emulate a guest instruction set and to allow the VM to be ported to different hosts architectures easily.

#### 1.8.2 Terra Trusted Virtual Machine

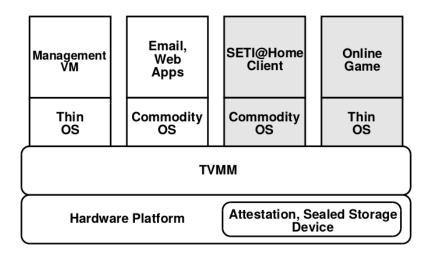

Terra [6] is a trusted virtual machine which solved the problem of how applications are secured on a modern operating system. Operating systems usually contain millions of lines of code and applications built on top have to rely on the security of the operating system. Further applications running on these systems are often not securely isolated from each other. Another problem addressed by Terra is how applications can be authenticated to verify the identity of the program. At the heart of Terra is a Trusted Virtual Machine Monitor (TVMM), which partitions a single tamper-resistant, general-purpose platform in multiple isolated virtual machines. Terra provides the property to authenticate the software running in the VM to remote parties, hence the name trusted virtual machine monitor.

Figure 1.8: Terra [6]

As shown in the figure the TVMM runs directly on the hardware and each application can run on his own operating system. This offers much freedom to the developers. The applications are then authenticated by the TVMM and can communicated to other applications running on the TVMM in a secure way. Although this approach offers interesting security features, the concept relies on powerful hardware and seems not to be an appropriate solution to run on secure chipsets.

#### **1.8.3** Virtual Machine for Microcontrollers

Virtual machines were also considered for microcontrollers [5]. To find a suitable virtual machine for microcontollers is not that trivial though. Therefore several small virtual machines were evaluated for this task. Microcontrollers have very small capacities, usually about 128-256K of flash memory and 128K of RAM. Therefore a virtual machine which performs well on a microcontroller would also be a good candidate as a virtual machine for secure chips. In the paper several VMs are evaluated.

| Virtual Machine          | Estimated Code Footprint |

|--------------------------|--------------------------|

| Java SE 6                | 68 MB                    |

| Java SE Embedded         | $29.5 \mathrm{MB}$       |

| Java J2ME—CDLC           | 128  KB                  |

| Java Card                | 256 KB                   |

| .NET Compact Framework   | $5.5 \mathrm{MB}$        |

| .NET CLI (Mono)          | $4 \mathrm{MB}$          |

| .NET Micro Framework     | 200 KB                   |

| Squawk (Java derivative) | 149 KB                   |

| Dis (Inferno)            | 311 KB                   |

| Parrot                   | 322  KB                  |

| LLVM                     | 1,336 KB                 |

| LUA                      | 109 KB                   |

| eLUA                     | 219 KB                   |

| Squirrel                 | 106 KB                   |

| PICOBIT                  | 15.6 KB                  |

| P-Code (Standard Pascal) | 28  KB                   |

| M-Code (Modula-2)        | 16 KB                    |

Table 1.2: Virtual Machines for Microcontrollers

From the virtual machines listed in the Table 1.2, all larger VMs were excluded and seen as no good fit for microcontrollers. Further it was stated that all Java VMs included only a subset of the Java standard and preprocessing of the images running on the VM is often required. All VMs for dynamic scripting languages were also excluded from their consideration. Dynamic scripting languages are not considered suitable for microcontrollers as the programs running on the controller depend on precise CPU cycles. This led at the end only to Modula-2 and Pascal variants as candidates. Modula-2 was eliminated because of unpopularity of the language and the lack of tools available. At the end they choose to use the Pascal P5 VM (P-Code).

In the first step they ported the VM to the microcontroller architecture. This involved several steps and modifications of the C code of the VM where necessary. In later steps they also included optimization of the VM which improved the speed. Before the improvement the VM on the microcontroller was 275 times slower compared to the native implementation of the applications. After the optimization the program was able to spend only 7.4 times more than the native application.

The VM considered in this paper has a very small footprint and could also be interesting for secure chips. For our approach, Pascal was not considered as a suitable language to develop applications for the secure chip though. Further the process of porting the Pascal VM seems very complicated and not straight forward. The goal of our VM is easy portability.

#### **1.8.4** Tiny Virtual Machine for Sensor Networks

Maté [9] is a VM designed for small wireless sensor devices. It runs on top of a small operating system called TinyOS. The main goal of Maté is to reduce the size of the applications running on the device. This allows to reduce the energy cost when new programs have to be transmitted to the devices. To achieve this Maté understands only 24 instructions which are tailored to the needs of applications in sensor networks. This allows to create complex programs with sizes under 100 bytes.

Although this concept is very good for applications in sensor network, it is very limited in the field and offers not enough diversity. Further, applications have to be written with the instructions understood by Maté and can not be written in C and then compiled.

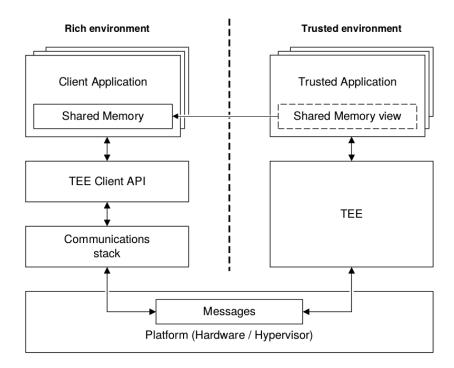

#### 1.8.5 ARM TrustZone

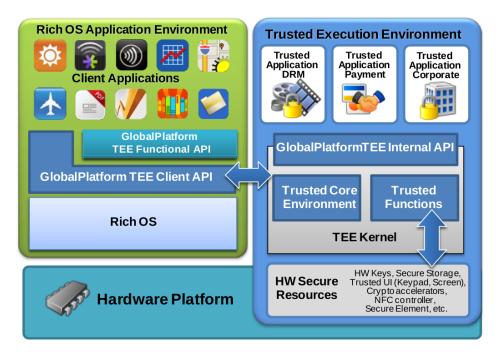

ARM defined an approach how security can be implemented on a System on a Chip (SoC). ARM TrustZone is part of version 8 of the ARM instruction set and provides a Trusted Execution Environment (TEE). TEE is discussed in Section 2.4. SoC vendors and OEMs can implement the framework according to a reference implementation which is provided open source by ARM.

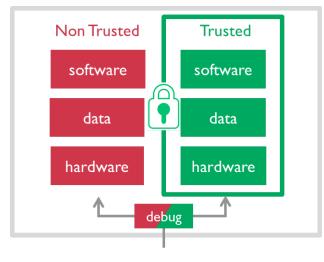

The concept of TrustZone is to have a secure and a non-secure world where the hardware is isolated from each other. A software runs either on the secure world or in the non-secure world and they can communicate with each other over a secure monitor. With hardware isolation not only CPU is isolated but also memory, bus and peripheral interfaces. Typical applications of the TrustZone are DRM implementations, secure key storage, mobile payment and authentication mechanisms. Applications which run in the trusted zone (secure world) are called Trusted Apps and are considered to be secure against software and hardware attacks.

Figure 1.9: ARM TrustZone [11]

Compared to external hardware security modules such as smart cards, the TrustZone offers a more flexible solution. External hardware security modules are very secure but offer only limited functionality. A smart card has only access to assets on the smartcard itself and can not directly interact with other components of the system. For example, it is not possible to directly secure user interfaces. Another disadvantage of the smartcard solution is the low processing performance available. The specifications of such devices are in the region of 5-20 Mhz with only limited amount of memory. This characteristics limit the range of applications.

Internal hardware modules are located on the SoC itself and consist of isolated components to the general purpose processing engine. It is also possible that the same general purpose components are used for the security module including a hardware logic component which prevents unauthorized access to sensitive resources. This systems have a big performance and cost advantage compared to the smart card solution. But still due to the isolation they often offer only a limited amount of functionality, like key management and some basic cryptographic operations.

In TrustZone the secure and non-secure world reside on the same processing units. Each processor has a secure and a non-secure part. For example a SoC with 4 processors has 4 non-secure and 4 secure worlds. A monitor software distributes then the resources.

The concept of TrustZone is very flexible but due to this flexibility exposes also many attack vectors. TrustZone implementations of Qualcomm have been proven to be vulnerable [13]. Qualcomm is used by many Android phone manufacturers and vulnerabilities in those chips offer the possibilities to attack millions of phones.

A further problem of the Qualcomm solution was that the images for the secure world are not encrypted. This allowed researchers to reverse engineer the code and find attack vectors in the code.

ARM TrustZone is an interesting concept for secure applications but are limited to ARM Architecture chips. In the world of STBs many different chip vendors are present. The CAS vendor would rely that each chip vendor implements ARM TrustZone. Our solution on the other hand tries exactly to cicrumvent this problem. Moreover, our virtual machine could be used as abstraction layer on top of the ARM TrustZone.

### Chapter 2

### Background

For the abstraction layer between the secure chip and the application running on the chip we will create a virtual machine. The concept of virtual machines is closer discussed in this chapter. Further we discuss the instruction sets we considered for our virtual machine. Additionally, we also give some detailed information about Trusted Execution Environment (TEE). Some secure chip manufacturers, for example ST, implement the TEE standard to provide an interface between unsecure applications and secure applications running on the secure chip.

#### 2.1 Virtual Machines

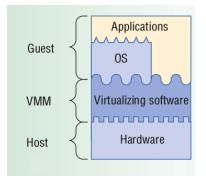

In early stages of computer development, the hardware was designed first and the software was later developed specifically for the hardware. These programs where quite simple but could not be interchanged to other hardware architectures. Quickly, it became evident that software compatibility and portability is very important. To accomplish this, the Instruction Set Architecture (ISA) was introduced. The ISA defined the interface between hardware and software precisely and allowed to run programs on different hardware if the same architecture was supported. This was already a big improvement. The problem still existed though that different ISAs emerged and programs compiled for one ISA could not be run on hardware of another architecture. In addition, operating systems were developed which manage the hardware resources and allow simplification of writing applications which run on top of the operating system. The operating system therefore exposes interfaces to the application developers. This added another problem that programs written for one operating system can not be used on a different operating system. This limitation can be circumvented with the help of a Virtual Machine (VM) [14]. The VM adds another layer between the underlying platform and the software to be executed. The VM thereby appears to the software as the platform required to run the program. This can either be a specific ISA or a full operating system.

In Figure 2.1 such a layer is shown between the hardware and the operating system and application. We shall name this layer virtualizing software or Virtual Machine Monitor (VMM). As shown in the figure the application which needs to be executed either uses the Application Binary Interface (ABI) interface of the operating system or an privileged instructions to access hardware resources. The VMM intercepts privileged instructions to manage shared access to hardware resources. For the guest application it seems a direct call to the hardware resource was performed. Additionally the VMM virtualizes the ISA which is expected by the operating system and the application. We define the platform on which the VMM runs the *host* platform which provides the host ISA. The operating system or application which runs on top of the VMM we define as the *guest* system. Guest applications therefore expect the guest ISA.

Figure 2.1: Virtual Machine Composition [14]

Virtualisation is only one application of virtual machines. The four major task of VMs are:

- Emulating: The Host system has a different ISA or ABI than the guest system. The Virtual Machine can either emulate the Guest architecture on top of the Host system or translate the Guest architecture to the Host architecture.

- **Optimizing:** The Virtual Machine interprets the Guest software and can include optimization on various kind of vectors like decrease the memory footprint or reduce the amount of executed instructions by taking implementation specific information into consideration.

- **Replication:** Given a single Host platform, a Virtual Machine can allow to run multiple Guest systems at the same time. Through virtualisation of resources each Guest system can be decoupled of the other Guest system. But also sharing of resources to several Guest systems is a possibility.

- **Composing**: By combining the various types of Virtual Machine we can provide execution platforms to flexible systems.

For our solution we mainly focus on the emulation part of the virtual machine. In this case the instructions of the secure applications are interpreted by the virtual machine and executed on the host chip architecture.

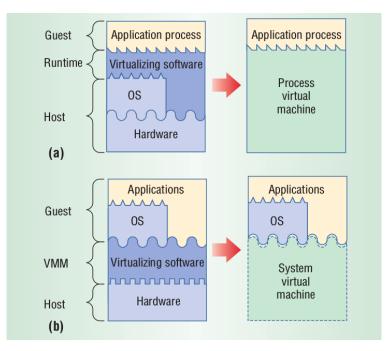

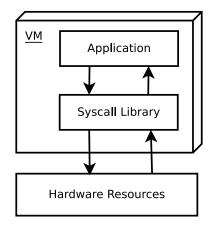

#### 2.1.1 Process And System VMs

In terms of virtual machines, we also make the distinction between process and system virtual machines. The two different concepts are shown in Figure 2.2. A process VM is only executed to support the process and terminated when the process is finished. An example is the Java VM, which is able to execute Java binary code in an individual process. The most common tasks for a process VM are replication, emulation and optimization. In a process VM, the virtualizion software is also called *runtime*.

System VMs, on the other hand, provide a complete environment in which many processes can coexist. This allows to run multiple guest operating systems simultaneously on a single host. The main task for system VMs is replication. In a system VM the virtualization software is also called *Virtual Machine Monitor* (VMM).

Figure 2.2: Process VM (a) and System VM (b) [14]

Our VM falls in the category of the process VM. The VM will be used to execute an application image and it is not intended to run several images at the same time.

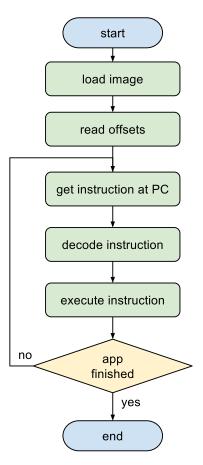

#### 2.2 Instruction Sets

The ISA is the interface between software and hardware. It is the visible part of the processor to the developer. A programmer can either implement a program for the processor by using the instructions or compile a program to the specific ISA. The instructions are then executed by the processor. Our VM is going to emulate a processor and therefore has to perform the same task as a real processor which executes the instructions.

To explain how instructions are executed we want to describe the most important parts which are used to execute an instruction:

- Central Processing Unit: Is the processor in a computer which performs the instructions. The three main components are the Arithmetic Logic Unit (ALU) to perform arithmetic and logic operations, registers to store results from the ALU and a control unit which is in charge of fetching and executing instructions.

- Arithmetic Logic Unit: Is the part in a Central Processing Unit (CPU) which performs arithmetic and logic operations such as add two numbers or bitwise AND two numbers. The result is either stored in the register or in the memory.

- General Purpose Register: Is a special part in the CPU to store information such as results from the ALU or pointers to regions in the memory. The general purpose register is usually used by ALU instructions for the parameters and the return value. The access of these internal registers is much faster than access of the memory which is outside of the CPU.

- Special Purpose Register: Other registers in the CPU have predefined tasks. For example the Program Counter (PC) keeps the address of the current instruction in the memory. The stack pointer (SP) points to the top of the stack. Other special registers may be used for overflow flags etc.

- Stack: Is a special region in the memory which is used to keep information about subroutines. For example when a function is called the parameters of the function and the return address, from where the function is called are pushed to the stack. The subroutine can then read the parameters from the stack and when it is finished use the return address to go back from the caller. As the name indicates the stack uses LIFO (last in first out) data structure. Usually the stack is initialized by the operating system and has a limit. A stack overflow happens when the stack limit is exceeded, for example when too many subroutines are called.

- Heap: Is a region in the memory which can be used by a program but is not structured. To use memory in the heap the program needs to allocate memory and free it when it is not used anymore. A memory leak is the situation when a program forgets to free the unused memory and therefore the region will not be available for other programs. These can lead that the whole memory is exceeded and the computer may crash.

The main tasks of the processor are fetching an instruction from the memory, decoding the instruction and executing the instruction. To perform all these tasks the registers, the ALU and the stack are utilized. Our VM emulates a processor and therefore has to perform the same tasks with a virtual register and stack. Where the input operands have to be stored to execute an ALU instruction is defined by the ISA type. Over time different versions where developed which used different components for calculations. The three most common types are:

- Stack ISA: The operands for the ALU are implicitly pushed to the stack. The ALU then performs the operations directly with the values from the stack.

- Accumulator ISA: Uses a special register, the accumulator, in the CPU to store one operand implicit. The ALU then can use this accumulator and another input value to perform operations.

- General Purpose Register ISA: All operands are mentioned in the instruction explicitly. They are stored either in the memory or on the register beforehand. The CPU offers for this several general purpose register which can be used. An architecture which allows that the operand is in memory or register is also called register memory architecture. An architecture which only allows operands to be in register is called register register architecture.

From the three above mentioned architectures the general purpose register architecture is the most successful one and is used almost exclusively in modern computers. Beside of differences where the operands are stored for the ALU, architectures also differ by instruction design. Two main architectures with different instruction designs are known today.

- Complex Instruction Set Computing (CISC): Is a processor design where a single instruction can execute several low level instructions at the same time. The design principle was to reduce the amount of instructions which the processor has to perform and support higher level programming constructs directly on instruction level. This has the advantage that less instructions are needed and the resulting program is smaller. These type of instructions sets have a large amount of instructions whereby instructions are added over time and have variable length. Further complex instructions can use several clock cycles in this architecture. This makes it difficult to optimize the order of the execution of instructions.

- Reduced Instruction Set Computing (RISC): Follows a different design principle than CISC. It was suggested that a smaller instruction set, where each instruction uses only one clock cycle, can easier be optimized and at the end achieves a better performance than a processor with CISC architecture. Therefore, the reduced instruction set was developed, whereby "reduced" does not refer to lesser instructions but the amount of work a processor has to perform compared to complex instructions. Another feature is that commonly RISC instructions have a fixed length which simplifies fetch, decode and execution logic on the processor. This allows to produce processors with less transistors compared

to CISC but more registers and increase internal parallelism. One drawback of the RISC architecture is that usually more instructions are needed to complete the same task as one complex instruction which results in larger application sizes.

As RISC instructions are in general smaller and simpler to decode, we decided to use this architecture for our VM. This will also help to keep the VM implementation small enough for our target processor.

#### 2.2.1 MIPS Instruction Set

MIPS stands for Microprocessor without Interlocked Pipeline Stages and is a reduced instruction set computer architecture (RISC) originally developed by researchers from the Stanford University which later on founded the company MIPS Technologies. MIPS is a register-register architecture in which operands have to be stored explicitly in the registers before they can be used by the ALU. To access the memory, load and store operations are needed. Over the years several versions were developed from MIPS I until MIPS V and later on MIPS 32 and MIPS 64. The original MIPS ISA I to V has been extended in a backward compatible fashion. That means all MIPS I instructions where also valid in MIPS II to V. This had the advantage that programs which run on a MIPS I processor, run also on a MIPS V processor. 64-bit integers and addresses were added in MIPS III. MIPS was first intended for computer like environments but later on had more success in the embedded market. Embedded systems have different requirements in regard to memory usage and performance. MIPS 32 and MIPS 64 are intended to address this needs. MIPS 32 was then based on MIPS II, which did not support any 64 bit instructions, and MIPS 64 on MIPS V.

For simplicity reasons we decided to implement MIPS I ISA in our VM which consists of 61 instructions. For this reason when a program for the VM is compiled, we have to specify that only MIPS I instructions are allowed. The MIPS I instructions are defined in the reference manual [7] from MIPS. All instructions which are included in MIPS I and are implemented in the MIPS VM are listed in appendix A.

#### **MIPS** Registers

| Number | Name      | Usage                              |

|--------|-----------|------------------------------------|

| 0      | \$zero    | constant value 0                   |

| 1      | \$at      | reserved for the assembler         |

| 2-3    | v0-v1     | values for results and expressions |

| 4-7    | \$a0-\$a3 | arguments (procedures / functions) |

| 8-15   | \$t0-\$t7 | temporaries                        |

| 76-23  | so-s7     | saved                              |

| 24-25  | \$t8-\$t9 | more temporaries                   |

| 26-27  | \$k0-\$k1 | reserved for the operating system  |

| 28     | p         | global pointer                     |

| 29     | \$sp      | stack pointer                      |

| 30     | \$fp      | frame pointer                      |

| 31     | \$ra      | return address                     |

|        |           |                                    |

MIPS has 32 registers. The registers are used by the current executed instruction to store parameters and return values, but also to store pointers to the stack etc.

Table 2.1: MIPS registers

The registers and their usage are listed in Table 2.1. Register 4-7 (a0-a3) are used to pass the first four function parameters. All subsequent parameters of the function call are passed through the stack. The return values of the function are stored in register 2-3 (v0-v1). For 32 bit values only register 2 is used. For

64 bit return values, both return registers are used. The stack pointer is set to the top of the stack at the beginning of a program and grows down when values are added to the stack.

#### **MIPS** Instructions

MIPS I includes 61 instructions which we can be divided in four categories. Load and store instructions, arithmetic and logic operations, jump and branch instructions and miscellaneous instructions.

Load and Store instructions: In a CPU the access to a register is much faster than the access to memory. Therefore operational instructions only use parameters in the register. To prepare the data in the registers for the operational instructions, load instructions are used. To store the results from the operational instruction back to the memory, store instructions are used. An example of a load instructions is the load binary (LB) instruction as shown in Table 2.2. The parameters of the instruction are used to calculate the address in the memory where the data has to be loaded from. For the LB instruction the base address and an offset are added together to calculate the address. The byte in the memory at the calculated address is then stored in the target register, which is another parameter of the instruction. After the instruction finishes successfully, the program counter (PC) is advanced by four. During the next cycle of the CPU the next instruction will be read where the new PC points to. Load and store instructions are available for different data types. The instructions which load a byte (8 bits), a halfword (16 bits) or a word (32 bits) are listed in Table A.1. For double words (64 bits) two instructions are needed which load the left and the right part separately. They are listed in Table A.2.

| Instruction | LB rt, offset(base)                                       |  |  |  |

|-------------|-----------------------------------------------------------|--|--|--|

| Parameters  | ers rt: target register to store the byte from the memory |  |  |  |

|             | offset: from base address                                 |  |  |  |

|             | base: base address in memory                              |  |  |  |

| Operation   | REG[rt] = MEM[base + offset]                              |  |  |  |

| Advance PC  | 4                                                         |  |  |  |

Table 2.2: MIPS load binary instruction

**ALU instructions:** Arithmetic and logical instructions can operate on operands stored in the registers or use immediate constant operands. An example of an ALU instruction is the add word instruction (ADD), shown in Table 2.3. The instruction has three registers as parameters where two registers are used as the summands and the third register is used to store the addition. The program counter is advanced by four after the operation. Instructions which use an immediate operand are listed in Table A.3. Instructions for which all operands are in the register are listed in Table A.4. In Table A.5 all shift instructions are listed and in Table A.6 all multiply and divide instructions.

| Instruction | ADD rd, rs, rt                                   |

|-------------|--------------------------------------------------|

| Parameters  | rs: register of the first summand                |

|             | rt: register of the second summand               |

|             | rd: register to store the result of the addition |

| Operation   | REG[rd] = REG[rs] + REG[rt]                      |

| Advance PC  | 4                                                |

Table 2.3: MIPS add word instruction

Jump and Branch instructions: Jump and Branch instructions change the program counter to a new address of the program and can depend on conditions. An example of a branch instruction is given in

| li  | \$v0, | 1 | <pre>// load identifier to register V0</pre> |

|-----|-------|---|----------------------------------------------|

| li  | \$a0, | 2 | <pre>// set first parameter to 2</pre>       |

| li  | \$a1, | 4 | <pre>// set second parameter to 4</pre>      |

| sys | call  |   | // system call to vm                         |

|     |       |   | Listing 2.1: MIPS system call instructions   |

Table 2.4. The branch on equal instruction (BEQ) has two register and an offset as parameters. The offset is used to calculate the target address. The new target address is the program counter of the instruction after the branch instruction, also called delay slot, plus the shifted offset. The instruction in the delay slot is first executed before the program branches to the calculated target address. All jump and branch instructions are listed in Table A.7.

| Instruction | BEQ rs, rt, offset                                 |  |  |  |

|-------------|----------------------------------------------------|--|--|--|

| Parameters  | rs: first register for comparison                  |  |  |  |

|             | rt: second register for comparison                 |  |  |  |

|             | offset: offset to calculate the target address     |  |  |  |

| Operation   | if REG[rs] == REG[rt] then PC = PC + (offset << 2) |  |  |  |

Table 2.4: MIPS branch on equal instruction

**Miscellaneous instructions:** Miscellaneous instructions include only the NOP and system call instruction, as shown in Table A.8. NOP instructions do not perform any action and are used in MIPS I to delay instructions. This is needed because in a MIPS I processor after a value has been loaded into the register, it can not be accessed immediately with the next instruction. A delay has to be added to between loading and accessing the value.

MIPS system call The system call instruction is a special trap instruction which allows to access services from underlying hardware or for example from the kernel. For our VM we use system calls to enable access to hardware modules such as cryptographic operations. All system calls have a predefined number or identifier and can use various amounts of parameters. In MIPS the system call instruction is called syscal1 and does not include any parameters. Before the syscal1 instruction is called, the identifier and the arguments of the system call have to be stored in the registers so they can be used by the service which is called. An example is given in Listing 3.5. First the identifier 1 is stored in the register \$v0. Afterwards two arguments are stored in registers \$a0 and \$a1. Only then the syscal1 instruction is called. In our case the call is then handled by the VM which expects the identifier and arguments in the correct registers. The system call handler in the VM then executes the call according to the identifier in register \$v0.

#### **MIPS** Instruction Encoding

The encoding of instructions defines how the processor decodes the 32 bit values to the correct instruction. All MIPS I instructions are 32 bit long in which some of the bits define the instruction type. The remaining bits are used for parameters which can be used by the instruction itself. The 6 most right bits are called opcode. The opcode alone sometimes already defines the exact instruction. If the opcode is 000000 the instruction belongs to the SPECIAL instruction class. For this instruction class bits 5 to 0 are used to identify the unique instruction. If the opcode is 000001 the instruction belongs to the REGIMM class. Instructions of this class are uniquely identified by the bits 20 to 16. In Table 2.5 an example is given for an instruction which can be identified with just the opcode. The branch on equal (BEQ) instruction has opcode 000100. Bits 25 to 21 are used for the rs parameter, bits 20 to 16 for the rt parameter and the offset is defined by bits 15 to 0. All instructions which are uniquely identifiable with the opcode are listed in Table B.1.

| bits   | $31 \dots 26$ | $25 \dots 21$ | $20 \dots 16$ | $15 \dots 0$ |

|--------|---------------|---------------|---------------|--------------|

| name   | opcode        | rs            | rt            | offset       |

| values | 000100        |               |               |              |

Table 2.5: MIPS BEQ instruction encoding

A SPECIAL instruction is shown in Table 2.6. The ADD instruction has bits 5 to 0 set to 100000. Bits 25 to 21 are used for the rs parameter, bits 20 to 16 for the rt parameter and bits 15 to 11 for the rd parameter. Bits 10 to 6 are not used in this encoding. The instructions in Table B.2 show all SPECIAL instructions where the opcode is 000000.

| bits   | 31 26   | $25 \dots 21$ | $20 \dots 16$ | $15 \dots 11$ | $10 \dots 6$ | $5 \dots 0$   |

|--------|---------|---------------|---------------|---------------|--------------|---------------|

| name   | SPECIAL | rs            | rt            | rd            |              | function code |

| values | 000000  |               |               |               | 00000        | 100000        |

| Table 2.6: MIPS SPECIA | ADD instruction | encoding |

|------------------------|-----------------|----------|

|------------------------|-----------------|----------|

The branch on greater than or equal to zero (BGEZ) instruction belongs to the REGIMM instruction class. The encoding of this instruction is shown in Table 2.7. The bits 20 to 16 are 00001 and bits 25 to 21 are used for the rs parameter and bits 15 to 0 for the offset. The remaining REGIMM instruction are listed in Table B.3.

| bits   | 31 26  | $25 \dots 21$ | 20 16         | $15 \dots 0$ |

|--------|--------|---------------|---------------|--------------|

| name   | REGIMM | rs            | function code | offset       |

| values | 000001 |               | 00001         |              |

#### 2.2.2 ARM Instruction Set

Advanced RISC Machine (ARM) is a family of RISC architectures for processors developed by the company ARM Holdings. The company license the architecture to other manufacturers who design their own products. Chips with the ARM architecture were especially successful in the embedded market and are the most used chips in smartphones currently. The ARM architecture evolved over time and after version 7 three different architecture profiles were created.

- A-Profile: Application profile, implemented by Cortex-A chips for high performance.

- **R-Profile:** Real-time profile implemented by Cortex-R chips for real-time and safety critical applications.

- **M-Profile:** Microprocessor profile implemented by the Cortex-M chips for microcontroller and space critical applications.

Even though the segregation of the profile was introduced only after version 7, a special version ARMv6-M was introduced which only included a subset of the instructions of version 7. This allowed the manufacturing of even smaller processors with the name Cortex-M0. In ARMv6-M most instructions are 16 bit instructions, which are called thumb instructions. This allows to reduce the code sizes of an ARM program. All ARMv6-M instructions are explained in detail in the reference manual [10].

We choose to implement the ARMv6-M instruction set for our VM which will allow to create smaller images. For simplicity reasons our VM will support the same instructions as the Cortex-M0 chip. All ARM instructions which are implemented in our VM are listed in Appendix C.

#### **ARM Register**

ARMv6-M uses 16 registers of which some are used for a special purpose and some are general purpose registers. The registers are depicted in Table 2.8.

| Number | Name    | Usage                                 |

|--------|---------|---------------------------------------|

| 0-2    | a1-a3   | Function Arguments                    |

| 3      | a4      | Function Return Value                 |

| 4-8    | v1-v5   | Variable Register                     |

| 9      | v6/SB   | Platform Register                     |

| 10     | v7      | Variable Register                     |

| 11     | v8 / FP | Frame Pointer                         |

| 12     | IP      | Intra-Procedure-call scratch Register |

| 13     | SP      | Stack Pointer                         |

| 14     | LR      | Link Register                         |

| 15     | PC      | Program Counter                       |

Table 2.8: ARM Registers

Registers 0-2 (a1-a3) are used for the first three function arguments. Any further arguments are passed through the stack. The return value of the function is stored in register 3 (a4). The variable registers (v1-v7) can be used for storing values which then are accessible for other instructions like add or sub. Register 9 and 11 can either be used as variable register or as a platform register for register 9 or as a frame pointer for register 11. The platform register requires that the value held is persistent across all calls. The frame pointer is used to point to local variables on the stack across function calls. Register 12 is normally used to store values between subroutines. The stack pointer points to the stack position and changes for each subroutine. The link register holds the link to the caller position and the program counter hold the current position.

#### **Application Program Status Register**

ARM uses also special status register called Application Program Status Register. The register is 32 bit long but only 4 bits are used. The reserved 28 bits are allocated for system features of future extensions. The 4 used bits are used as flags which are validated in some instructions if certain conditions are met.

| Bit | Name | Usage                   |

|-----|------|-------------------------|

| 31  | Ν    | Negative Condition Flag |

| 30  | Ζ    | Zero Condition Flag     |

| 29  | С    | Carry Condition Flag    |

| 28  | V    | Overflow Condition Flag |

Table 2.9: ARM Application Program Status Register

The Negative Condition Flag is set when the result, for example of a subtraction, is negative. Otherwise it is set to zero. The Zero Condition Flag is set when the result is zero and set to 0 otherwise. A result of zero indicated often the result of a comparison. The Carry Condition Flag is set to 1 if the instruction results in a carry condition, for example an unsigned overflow on an addition. The Overflow Condition Flag is set to 1 if the instruction results in an overflow condition, for example a signed overflow on an addition.

#### **ARM Instructions**

The Cortex-M0 chip supports 78 instructions which are devided in five categories, branch instructions, dataprocessing instructions, status register access instructions, load and store instructions and miscellaneous instructions.

**Branch Instructions:** These instructions are used to change the program counter to a new address. The branch instruction (B), shown in Table 2.10 is an example. The instruction has as parameter an immediate value which is used to calculate the target address. The operation of the instruction includes to add the immediate value to the current program counter. All branch instructions are listed in Table C.1.

| Instruction | B imm                                            |

|-------------|--------------------------------------------------|

| Parameters  | imm: immediate value to calculate target address |

| Operation   | PC = PC + imm                                    |

Table 2.10: ARM branch instruction

**Data-processing instructions:** In ARM data-processing instructions include arithmetic and logic instructions which in general have a destination register where the result of the instruction is stored. The operands for the instruction thereby can be immediate, where the operand is a constant, or in a register. An example where the operands are in the registers is shown in Table 2.11. The ADD instruction has three parameters where two are used for the summands and one is used for the target register where the results is stored. In ARM during the ADD instruction also the Application Program Status Register (APRS) flags are set accordingly. These flags may be used by a following branch instruction. All data-processing instructions are listed in Table C.2.

| Instruction | ADD rd, rn, rm                               |  |  |

|-------------|----------------------------------------------|--|--|

| Parameters  | rd: destination register to store the result |  |  |

|             | rn: register with the first summand          |  |  |

|             | rm: register with the second summand         |  |  |

| Operation   | REG[rd] = REG[rn] + REG[rm]                  |  |  |

|             | set APSR Flags                               |  |  |

Table 2.11: ARM ADD instruction

**Status register access instructions:** The instructions listed in Table C.3 move the contents of the APRS to or from the general purpose register. An example is the move to register from special register (MRS) instruction shown in Table 2.12. The instruction has two parameters, the destination register and the special register value. The special register value has a special encoding which allows to access the APRS register but also other special registers. All status register access instructions are shown in Table C.3.

| Instruction | MRS rd, sr                                   |  |  |

|-------------|----------------------------------------------|--|--|

| Parameters  | rd: destination register to store the result |  |  |

|             | sr: special register to read                 |  |  |

| Operation   | REG[rd] = read special register (sr)         |  |  |

Table 2.12: ARM MRS instruction

| MOVS | a1, #2 | <pre>// set first argument to 2</pre>             |

|------|--------|---------------------------------------------------|

| MOVS | a2, #4 | // set second argument to $4$                     |

| SVC  | #1     | <pre>// system call to vm with identifier 1</pre> |

|      |        | Listing 2.2: ARM system call instructions         |

Load and store instructions: Load and store instructions are used to load data from the memory to the register which then can be used by data-processing instructions and to store the result back to the memory. Single load instructions, which only load data from one address, are listed in Table C.4. Instructions which load and store multiple rows, are listed in Table C.5. An example is the load register (LDR) instruction which has two parameters, the target register and an immediate value as shown in Table 2.13. The address from where the data has to be loaded is calculated with help of the value in register 13 and the immediate value. Then the data at the calculated address is read and stored in the target register. Other examples of load and store instructions are the PUSH and POP instructions. These instructions are used during branching to push the current registers to the stack and pop the information back to the registers when the branch ends.

| Instruction | LDR rt, imm                                        |

|-------------|----------------------------------------------------|

| Parameters  | rt: target register to store the value             |

|             | imm: immediate value to calculate the load address |

| Operation   | address = REG[13] + ( imm << 2)                    |

|             | REG[rt] = MEM[address]                             |

Table 2.13: ARM LDR instruction

**Miscellaneous instructions:** Miscellaneous instructions include special instructions such as supervisor calls, which are the system call of ARM. Many of the instructions are hardware related, such as WFE and are not implemented by our VM. All miscellaneous instructions are listed in Table C.6. The instructions which are not implemented are marked with (not supported).

**ARM system call** The system call instruction in ARM is called SVC. In contrast to the MIPS system call instruction, this instruction has one argument which is the identifier of the system call. The arguments of the system call need to be stored in registers a1 to a3. If the system call needs more arguments the stack has to be utilized. After the arguments are stored in the register, the system call instruction with the identifier can be called as shown in Listing 2.2.

#### **ARM Instruction Encoding**